High-Bandwidth, Low-Computational Approach: Estimator-Based Control for Hybrid Flying Capacitor Multilevel Converters Using Multi-Cost Gradient Descent and State Feedforward

Abstract

This paper presents an estimator-based control framework for hybrid flying capacitor multilevel (FCML) converters, achieving high-bandwidth control and reduced computational complexity. Utilizing a hybrid estimation method that combines closed-loop and open-loop dynamics, the proposed approach enables accurate and fast flying capacitor voltage estimation without relying on isolated voltage sensors or high-cost computing hardware. The methodology employs multi-cost gradient descent and state feedforward algorithms, enhancing estimation performance while maintaining low computational overhead. A detailed analysis of stability, gain setting, and rank-deficiency issues is provided, ensuring robust operation across diverse converter levels and duty cycle conditions. Simulation results validate the effectiveness of the proposed estimator in achieving active voltage balancing and current control with 6-level AC-DC buck FCML, contributing to cost-effective solutions for FCML applications, such as data centers and electric aircraft.

Index Terms:

flying capacitor multilevel converter (FCML), estimator-based control, active voltage balancing, state feedforward, multi-cost gradient descent method, hybrid estimatior, AC-DC buck conversion, datacenter power delivery.I Background

Hybrid flying capacitor multilevel (FCML) converters are attracting interest for their power efficiency, power density, lightweight structure, and scalability [1, 2, 3, 4].

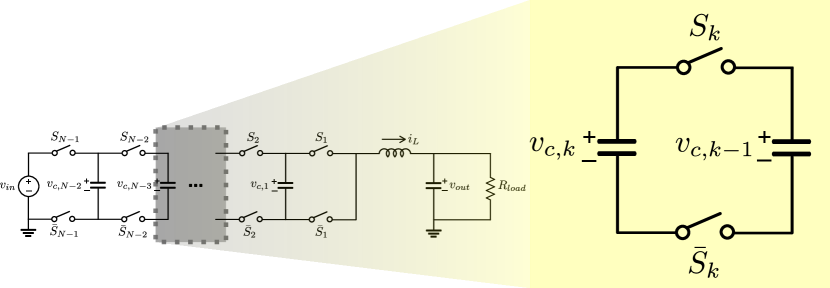

An -level hybrid FCML converter employs flying capacitors to evenly distribute voltage stress across lower-voltage switches. As shown in Fig. 1, the voltage across the -th flying capacitor, where , is maintained at , with each switch experiencing a voltage stress of [5]. The FCML topology also effectively spreads switching losses across multiple switches, enhancing thermal management. Additionally, power density is increased due to the reduced filter size, scaling by a factor of [6]. Cascaded bootstrap gate drivers can further enhance the compactness of FCML hardware by removing the need for isolated DC-DC converters in gate drive circuits, contributing to reduced hardware complexity and design cost [7].

Utilizing the advantages of FCML, its applications are expanding across various fields. In spacecraft, FCML converters efficiently handle high voltage while maintaining a compact footprint, which is crucial for space-limited environments [8, 9]. Additionally, GaN-based eHEMT devices commonly used in FCML are radiation-hardened, ensuring reliable operation under high-radiation conditions encountered in space [10]. For electric aircraft, FCML’s high power density supports lightweight designs and efficient space utilization, enhancing both efficiency and control performance [11]. In data centers, FCML converters simplify the conventional two-stage step-up/down conversion process to single-stage step-down, reducing both system volume and complexity [12, 13, 14].

A challenge in hybrid FCML topology is ensuring voltage balance across the flying capacitors. Each switch pair experiences voltage stress (), as shown in Fig. 1, determined by the voltage difference between adjacent flying capacitors as follows:

| (1) |

where . This voltage balance must be maintained in all situations, including start-up, closed-loop operation, and shut-down.

During start-up and shut-down, both the input and flying capacitors must charge or discharge evenly; otherwise, voltage imbalances may arise, increasing the stress on switching devices and risking overvoltage failure. To prevent this, each capacitor—including the input and flying capacitors—must charge in specific voltage ratios [15, 16].

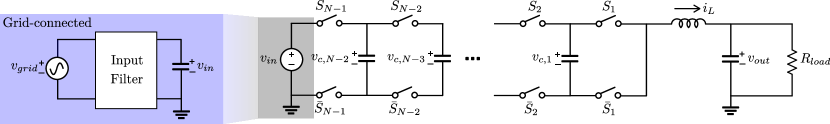

For example, in an AC-DC buck FCML for data center power delivery, as illustrated in Fig. 2, the start-up pre-charging process varies based on the output voltage condition. If the output voltage is connected to a 48V DC bus or pre-charged to 48V, a boosting algorithm (utilizing buck/boost duality) can charge the flying capacitors using the output energy. However, if the system must rely solely on AC power for initial charging, it is essential to limit inrush current through the input capacitor while ensuring adequate charging of the flying capacitors.

Additionally, voltage balancing is also essential during steady-state operation. For a DC input voltage that requires only maintaining DC flying capacitor voltage levels, passive balancing generally minimizes the control effort needed to sustain voltage balance. However, in grid-tied AC-DC buck converters, where oscillates at twice the line frequency, passive balancing alone cannot adequately maintain the correct flying capacitor voltage ratios, even under steady-state conditions [17]. The limited bandwidth of passive balancing increases the risk of overvoltage stress on switching devices. Consequently, a faster and more dynamic voltage balancing approach is necessary to ensure reliable operation and reduce the risk of device failure.

To achieve sufficient bandwidth, several methods for active balancing flying capacitor voltages have been introduced [18, 19, 20, 21]. One promising approach uses closed-loop active balancing control and differential-mode voltage is utilized for feedforward term in current controller, achieving fast voltage balancing without impacting current control [21]. This method offers higher bandwidth compared to conventional techniques. However, implementing the method requires isolated voltage sensors for each of the flying capacitors due to the floating nature of each node’s voltage relative to ground. The use of these isolated voltage sensors increases hardware complexity and cost.

To address these limitations, estimator-based control can be considered. The estimator-based control has become a widely adopted in power electronics field, such as motor control and grid-connected converters [22, 23]. By reducing the dependency on physical sensors, the estimator-based control offers cost-effectiveness and improved system reliability.

In literature [24], flying capacitor voltage estimation method has been proposed. Although this method avoids the need for high-cost control units and complex implementation (e.g., FPGA) as seen in [19, 25], it still presents certain challenges:

-

1.

The method requires dual CPU operation within the MCU, resulting in additional communication overhead, as well as higher CPU and peripheral resource consumption.

-

2.

Precise sampling and rapid computations on one of the CPUs at rates of several hundred kHz are necessary, imposing a significant computational load.

-

3.

It relies solely on pole voltage data, overlooking other available information that could enhance the estimation of flying capacitor voltage.

-

4.

The literature has focused on implementing real-time estimation without offering mathematical proof of stability or clear guidelines for setting control gains.

-

5.

The literature has focused solely on estimation without exploring estimator-based control.

This paper addresses key research gaps by proposing an high-bandwidth, low-computation solution that operates with a single MCU CPU, without requiring additional peripheral resources. The method achieves high-bandwidth estimation with reduced sampling and control frequencies by utilizing given plant dynamics, duty cycle, and sampled inductor current information. This approach can enhance the versatility of estimator-based control for hybrid FCML converters, supporting a broad range of applications. The estimator-based control enables high-bandwidth operations such as current control and active voltage balancing, comparable to the performance achieved with sensor-based control.

Furthermore, this study includes a mathematical analysis from an optimization perspective, covering time-scale separation in estimator-based control, gradient descent, and estimator gain setting. Additionally, it examines the feasibility of achieving full-rank operation for each level of FCML under specific duty constraints.

The remainder of this paper is organized as follows. Chapter II discusses a hierarchical control structure based on time-scale separation principle. With generalized proportional-integral-resonant (PIR) controller for estimator-based control, controller design considerations are addressed based on application requirements. Chapter III introduces the proposed flying capacitor voltage estimator and a related sampling method and provides proofs of observability and stability, along with an analysis of the rank-deficiency problem and guidelines for gain settings. Chapter IV presents the simulation results that verify the effectiveness of the proposed method. Chapter V is the conclusion.

II Estimator-Based Control: Hierarchical Controller Design and Considerations

II-A Time-scale Separation

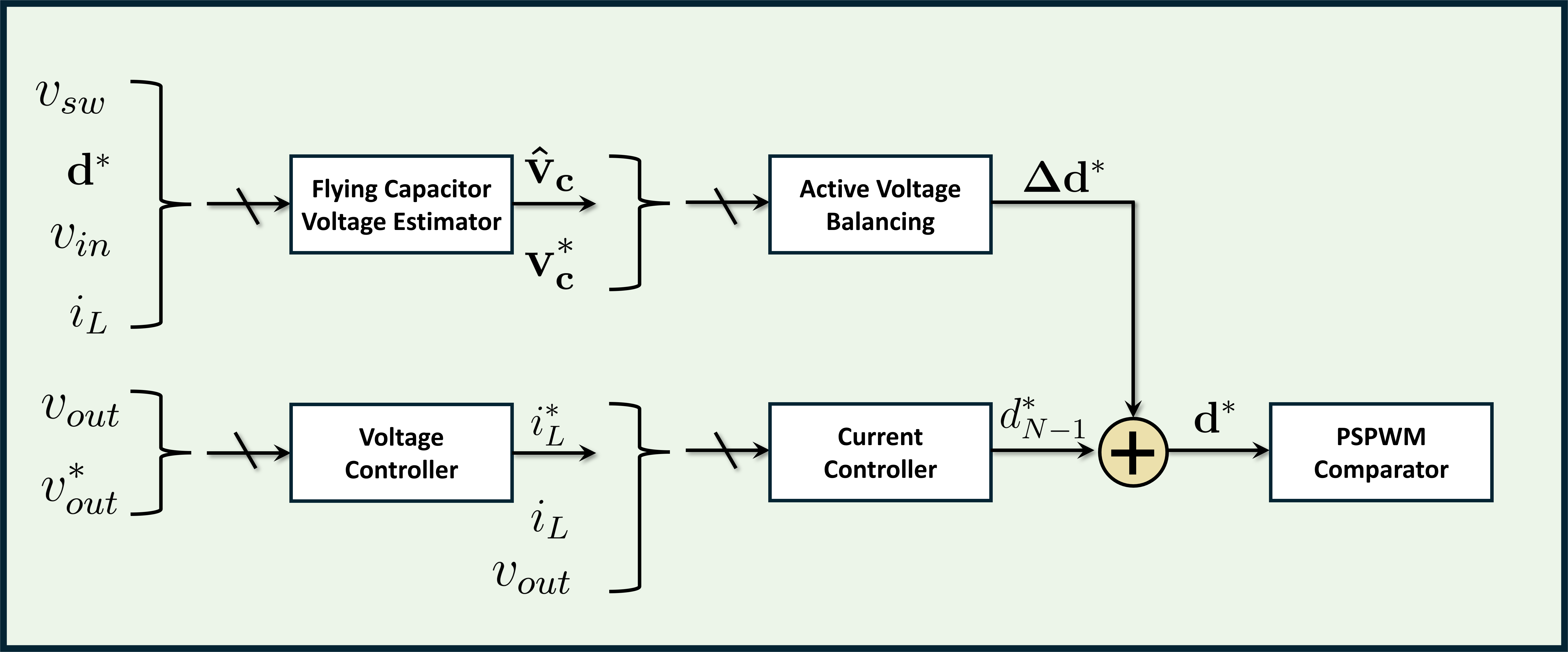

The hybrid FCML’s multivariable control objectives, including the flying capacitor voltages, output voltage, and inductor current, present a challenging control problem due to the multiple control inputs and outputs in this multi-inpue multi-output (MIMO) system. The design problem can be simplified by organizing controllers in a cascaded loop, as shown in Fig. 3. This setup allows each control layer to be designed independently:

-

•

The inner loop controller is assumed to have infinite bandwidth when designing the outer loop controller.

-

•

The outer loop estimator/sampler is assumed to have infinite bandwidth when designing the inner loop controller.

These assumptions are applied to FCML controllers and estimator as follows:

| (2) |

| (3) |

Here, the settling time, , is the inverse of the control bandwidth, . The subscripts , , , and represent the current controller, voltage controller, active balancing controller, and flying capacitor voltage estimator, respectively.

Meanwhile, in digital control systems, delays can arise that are not typically present in continuous-time systems. Control variables, such as inductor current, are sampled using a zero-order hold, and the pole voltage reference generated by the current controller introduces specific delays:

-

•

The reference is updated as a PWM comparator input in the next sampling period, introducing a one-sample delay.

-

•

The average PWM voltage is applied halfway through the sampling period, resulting in a cumulative delay of 0.5 sampling periods, which directly impacts the controller’s stability margin.

Therefore, the PWM pole voltage is effectively delayed by 1.5. To mitigate instability caused by these delays, the sampling period should be much shorter than the controller’s settling time, as indicated by:

| (4) |

where is the sampling period. According to the time-scale separation principle in (2), (3), and (4), each controller’s bandwidth can be maximized while time-scale separation principle minimizes stability impacts between control layers while ensuring a fast response.

| Symbol | Description | Explanation |

|---|---|---|

| Controller Input | Main input variable to the controller. | |

| Input Reference | Target or reference value for the input. | |

| Input Error | Difference between and . | |

| Anti-windup Input | Input used to limit integral windup effects. | |

| Controller Output | Main output variable from the controller. | |

| Output Reference | Target or reference value for the output. | |

| PIR Controller Output | Output from the PIR controller block. | |

| Feedforward Input | Direct feedforward input to the controller. | |

| Active Damping Input | Input used for active damping control. | |

| Final Output Reference | Saturated final output reference value. | |

| Anti-windup Switch | Enables/disables anti-windup function. | |

| Resonant Integrator Switch | Enables/disables resonant integrators. | |

| Integrator Switch | Enables/disables integrators. | |

| Controller Enable Switch | Enables/disables the entire controller. |

II-B Sampling

To reduce the impact of switching ripple in sampled inductor current, the sampling frequency is typically synchronized with the PWM carrier, with sampling taking place at the peak or valley of the PWM carrier [26]. For phase-shifted PWM (PSPWM), the sampling period () is therefore aligned with the PWM carrier period () as follows:

| (5) |

where is a positive integer.

Since the effective switching frequency of the FCML converter with PSPWM typically reaches several hundred kHz [27], and given the computational requirements per control cycle, the sampling and control frequencies are generally set between 10 and 40 kHz to ensure sufficient real-time processing capacity. The choice of sampling frequency is based on the computational load and the capabilities of the digital signal processor (DSP) in use; here, the TMS3202837xX CPU from Texas Instruments is considered.

II-C Generalized Proportional-Integral-Resonant Controller

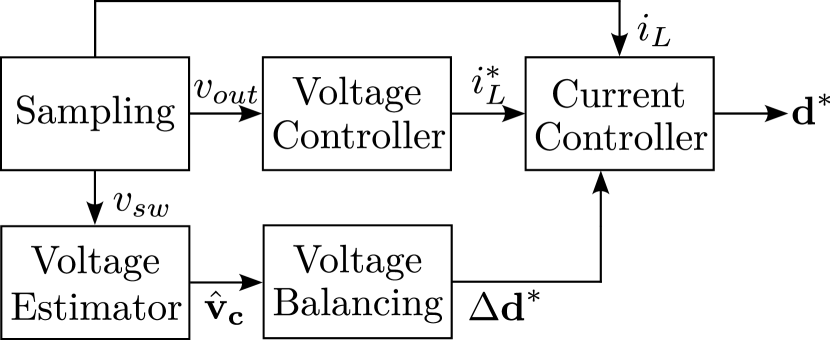

The following subsections outline the design of the controller and estimator for the FCML, with each controller following a generalized PIR (Proportional-Integral-Resonant) framework shown in Fig. 4. Each controller can be modified according to specific control objectives.

In this framework, and represent the input and output variables of the controller, respectively. Here, , , and stand for the input reference, input error, and anti-windup input, respectively, while , , , , and denote the output reference, PIR controller output, feedforward input, active damping input, and the final output reference. Control switches , , , and are used to enabling functions for anti-windup, resonant integrators, integrators, and the overall controller, respectively. For reference values, a superscript * is used throughout this paper. The following TABLE I summarizes this information for clarity.

The controller gain is set to match the desired bandwidth by appropriately placing poles in the Laplace domain, based on the closed-loop transfer function of the plant and controller. Detailed formula-based gain settings for each controller are skipped in this paper.

II-D Output Voltage Control

The control problem and the plant dynamic equation are:

| (6) |

| (7) |

, respectively. Here, , , and denotes the inductor current, output capacitance, and load resistance, respectively.

For DC/DC operation of the FCML [20], an integrator in the controller is essential to eliminate steady-state error when using a DC reference. However, during scenarios such as initial charging or sudden load changes, large voltage errors may push the voltage controller’s output beyond the current limit, which clamps the current reference and reduces the voltage controller’s effective bandwidth.

Additionally, during current reference clamping, error accumulation in the integrator can lead to overshoot or undershoot in the output voltage, even after reaching the target voltage . This, referred to as ‘integrator wind-up,’ can occur in any controller with an integrator and output clamping. To address this, an anti-windup mechanism can be applied to mitigate the the error accumulation. With these considerations, the voltage controller is designed as follows:

| (8) |

| (9) |

where represents the sign function, and is the maximum available inductor current.

For AC/DC boost operation (e.g., power factor correction), the only difference from DC/DC is the presence of an AC power flow component at twice the line frequency [6]. To control the DC output voltage, this AC power component can be filtered out by (, ), or current controller can have multi-resonant controller () to eliminate the odd harmonic current component from voltage controller.

For unity power factor operation, the current reference is multiplied by a unit sinusoidal waveform whose phase matches the grid phase using a phase-locked-loop (PLL). The output of controller with current limitation is as follows:

| (10) |

where is estimated grid phase from the PLL. denotes nominal angular frequency of grid.

For AC/DC buck operation with an output inductor [13, 14], two key points are noted:

-

•

Power transfer between the grid and the FCML only occurs when the grid voltage magnitude surpasses the output voltage (e.g., 48 V in data center applications)

-

•

The input voltage (grid voltage folded by rectifier) varies at twice the line frequency.

This results in both current and voltage containing DC and AC components with its harmonics. To manage these characteristics effectively, a proportional-resonant-integral (PIR) controller can be utilized as follows:

| (11) |

The controller’s output with current limitation is defined as follows:

| (12) |

Here, denotes the current reference waveform, which is synchronized with the grid voltage to ensure a high power factor. compensates for the effects of the input capacitor and filter on the grid current [14]. It is crucial to set with consideration for any amplitude increase resulting from .

Meanwhile, when , the FCML converter is unable to draw power from the grid. In this case, no control or estimation is needed, and all stored energy in the flying capacitors and inductors remains constant, except for the output capacitor, which is gradually discharged by the load. The controller can be disabled to prevent unnecessary operation and error accumulation in integrators as follows:

| (13) |

II-E Active Voltage Balancing

The control problem for flying capacitor voltages is defined as follows:

| (14) |

where denotes the flying capacitor voltage vector, is the scaling vector, and represents the duty cycle differences. Each element for , where is the PWM duty cycle of the -th switch shown in Fig. 2. Here, the hat symbol () denotes an estimated value.

All controllers adhere to the principle of time-scale separation; therefore by enforcing , the following plant equation for flying capacitor voltages can be considered:

| (15) |

where , and for . The averaged plant equation over a sampling period () becomes:

| (16) |

This indicates that changes in flying capacitor voltages () are influenced by both the duty cycle difference () and the inductor current (). Since is controlled by the output voltage controller, remains the only variable available for controlling . Therefore, the active balancing controller can be implemented simply with a proportional controller as follows:

| (17) |

| (18) |

It becomes necessary to limit with when low inductor current results in a large . Excessive can lead to a loss of inductor current control. prevents duty cycle saturation, thereby preserving stability in the current controller.

For AC/DC buck operation, which requires high-bandwidth active voltage balancing, maintaining accurate voltage balance becomes increasingly critical as the input voltage () rises, helping to minimize stress on switching devices.

In contrast, at lower levels, there is more tolerance for voltage imbalance, allowing minor control inaccuracies without major impact. Additionally, when is low, operates near its maximum duty cycle of 1, so can potentially cause to reach saturation. This occurs even though active balancing is less critical than current control under these conditions. With these considerations, the controller can be disabled as follows:

| (19) |

where provides a margin for disabling the active voltage balancing controller.

II-F Current Control

The control objective and plant equation for inductor current are defined as follows:

| (20) |

| (21) |

respectively. The time-averaged plant equation over a sampling period () is:

| (22) |

To reduce disturbances from the output voltage () and differential term of flying capacitor voltages, the following feedforward term () is applied:

| (23) |

For estimator-based control, estimated flying capacitor voltages () are used in the feedforward term, replacing as shown in [21]. A reduction in estimation bandwidth or an increase in estimation error may introduce disturbances, potentially degrading the current controller’s effective bandwidth. The disturbance effect on current control becomes more severe when inductor has lower inductance [23]. Therefore, a fast and accurate estimator is required for estimator-based control.

For DC/DC boost operation, an integral controller is required for eliminating the DC steady-state error of the current. The controller configuration is as follows:

| (24) |

For AC/DC boost operation, where the current is primarily a sinusoidal AC component, a resonant controller is preferable to achieve zero AC steady-state error:

| (25) |

In AC/DC buck operation for power factor correction, the inductor current may include both DC components and even harmonics of the line frequency, as noted in (12). This setup makes an integrator and a resonant integrator ideal choices for achieving unity closed-loop gain at specific frequencies. The current controller configuration for this case is:

| (26) |

For all cases, parameter variations, such as changes in inductor resistance, can affect the actual bandwidth of the current controller. To maintain precise control of the bandwidth, active damping is applied as follows:

| (27) |

Additionally, nonlinearities in the controller, such as output limits, anti-windup mechanisms, and output scaling with specific waveforms, can introduce instability or create limit cycles with harmonic generation [28]. This consideration is important for the implementation of all controllers and estimators. To prevent these nonlinear effects in the current controller, a high-gain proportional controller can be a practical alternative:

| (28) |

This configuration prevents wind-up issues by avoiding use of integrators in the current controller. It does not achieve unity gain at DC and exhibits lower gain as frequency increases. However, the integrator in the output voltage controller compensates by ensuring zero steady-state error for output voltage control.

To accurately regulate the output current based on from the voltage controller, the poles of the current controller should be placed for an overdamping response.

III Flying Capacitor Voltage Estimation

III-A Considerations for Estimator Implementation

In designing a state estimator, it is essential to ensure observability. This involves evaluating the number of variables to be estimated and verifying that the given system matrix has full rank. For an -level FCML converter, which has () flying capacitors, () independent equations are required to ensure a system matrix rank of ().

Secondly, once observability is confirmed with a full-rank, the implementation method must be considered in terms of computational load and estimation performance, which has explicit trade-off. The simplest approach for estimating is utilizing matrix inversion. However, as the number of levels in the FCML increases, the size of the state-space matrix grows significantly, containing at least elements.

Common matrix inversion algorithms have theoretical complexities ranging from to [29, 30]. For example, with , where , matrix inversion requires between approximately and operations. This rapid increase in computational load imposes a significant burden on the CPU of MCU. In industry, where low-cost CPUs are widely preferred, such processing demands are undesirable, as they would require a more complex and costly processing unit. This challenge highlights the need for computationally efficient estimation methods.

In [24], a method with a theoretical complexity of per sampling period was proposed to address the high computational load typically associated with matrix inversion. This real-time estimation technique offers an advantage by distributing computational complexity across multiple sampling instances rather than requiring full-rank conditions at each individual sample. As a result, it eliminates the need for matrix inversion while maintaining proper accuracy and bandwidth. Moreover, a balanced workload can be achieved by spreading calculations across control instances, making the computation easier to manage. However, the implementations of the method still rely on a high sampling rate and additional peripheral communication.

Finally, a well-designed estimator must utilize all available information to maximize the estimation performance. Fully utilizing the information improves the figure of merit for estimation, the superior balances can be found on the trade-off between the computational load and fast/accurate estimation.

In the proposed estimation method, the sampled current (), duty cycle reference (), and flying capacitor voltage () dynamics in (16) are utilized as new information. By incorporating this information, the estimation performance can be significantly enhanced, even with lower sampling and control frequency.

III-B Disjoint Sampling: Extracting Full-Rank System Equations

The pole voltage, a linear function of the flying capacitor voltages, is measured and used in the proposed estimator. A non-isolated voltage sensor can be utilized for this measurement. The pole voltage is sampled at the peak and valley of the PSPWM carriers, synchronously sampling voltage and current signals for control. At each sampling instance, estimator calculations are performed along with control operations, enabling estimation and control integration in a single control loop.

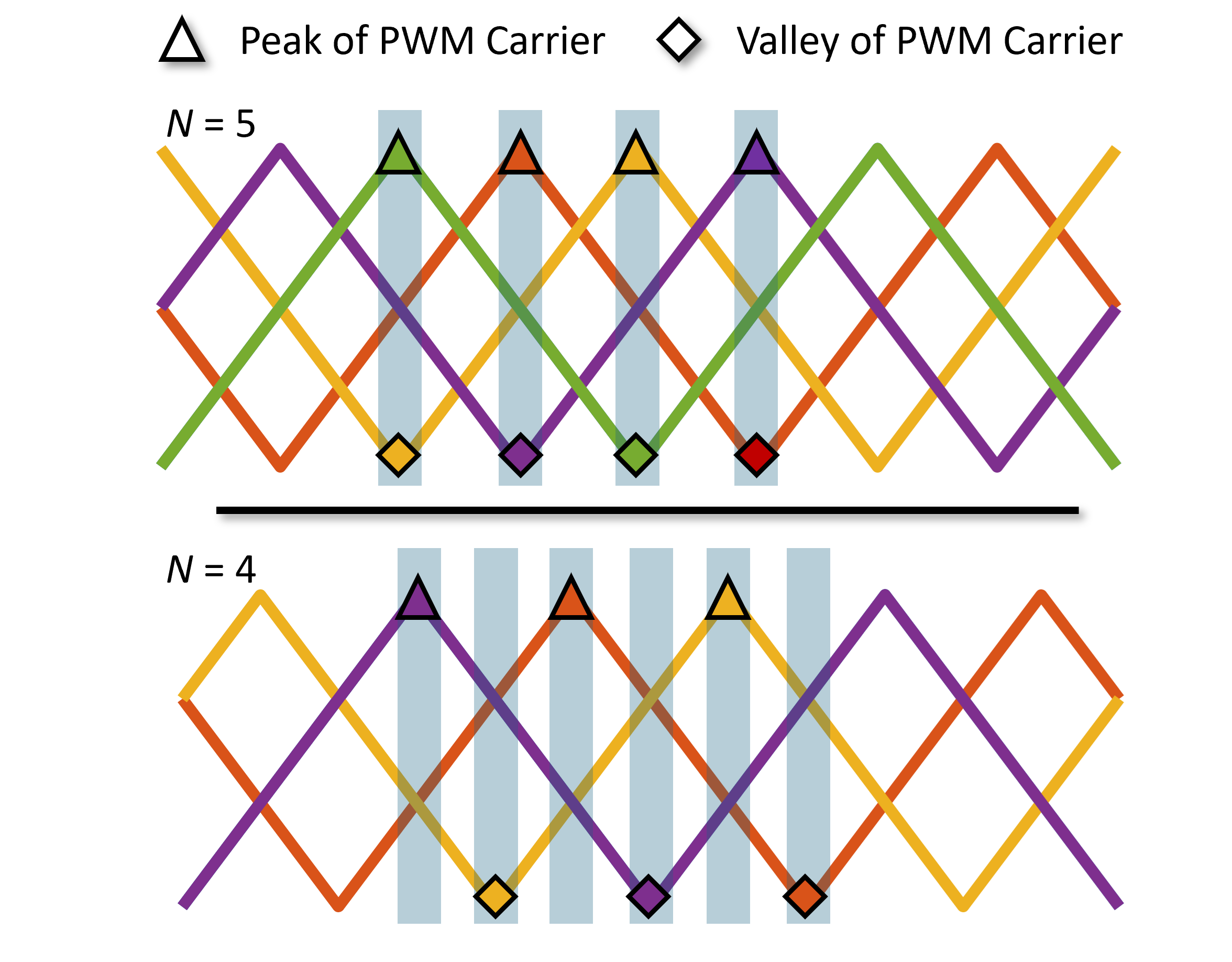

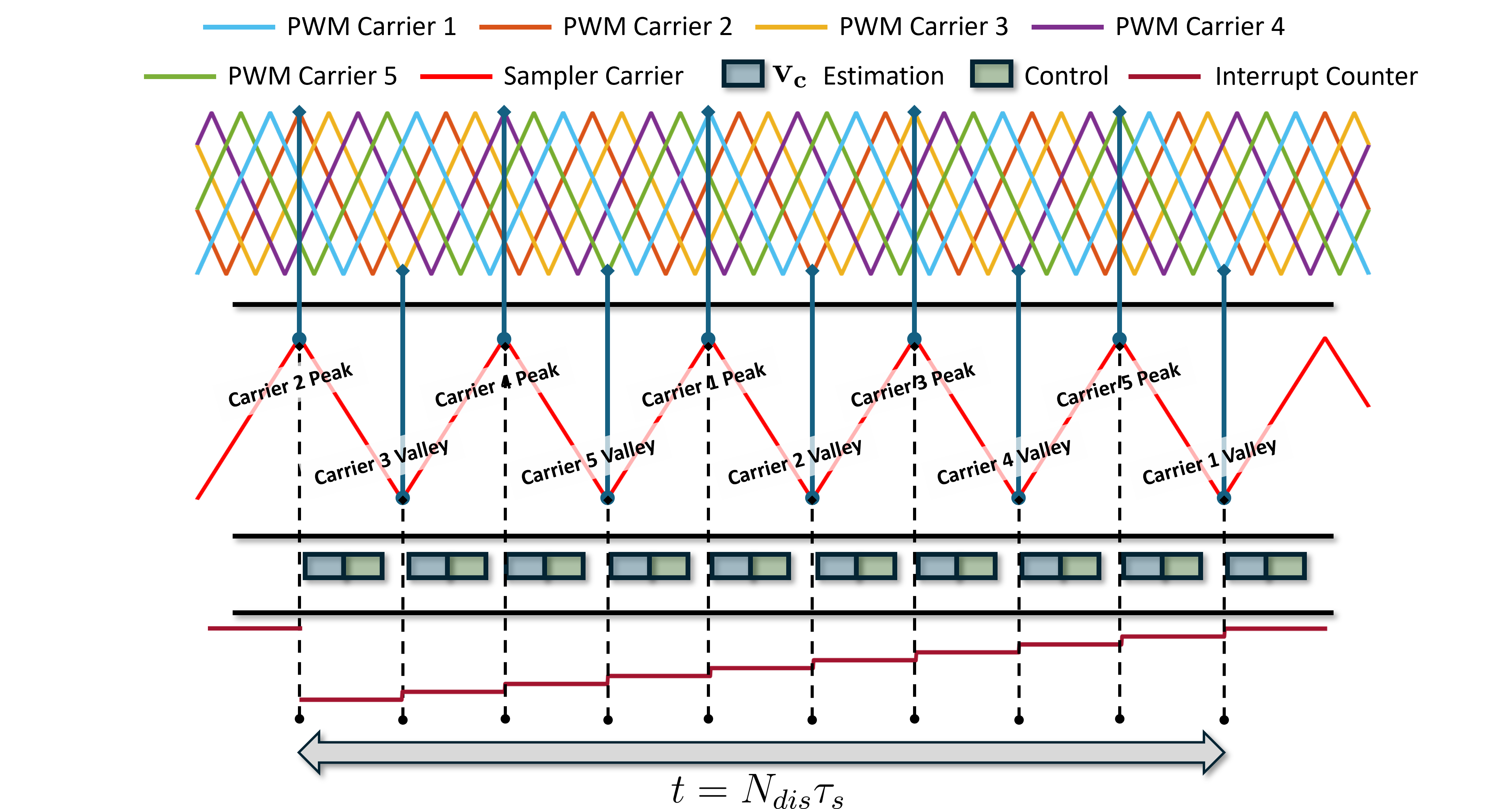

As shown in Fig. 5, for an odd-level FCML, different equations can be obtained during peak and valley sampling for the same duty reference under PSPWM, while for an even-level FCML, different equations can be obtained. The proposed disjoint sampling method shown in Fig. 6 uses a sampler carrier synchronized with PSPWM carriers, operating at a frequency of which is much lower than effective switching frequency . The number of different sampling instants () is defined as follows:

| (29) |

Sampling is triggered when the sampler carrier reaches its valley, incrementing the interrupt counter. To utilize disjoing sampling, in (5) is selected based on the following conditions:

| (30) |

| (31) |

The sampling frequency setting differs between odd-level and even-level FCML converters. This is because, as illustrated in Fig. 5, the even number of PSPWM carriers for odd-level FCML may result in one carrier’s peak coinciding with another’s valley.

Meanwhile, the proposed method will utilize a lower sampling rate compared to [24], which makes the estimator’s closed-loop bandwidth and accuracy degraded. While the proposed method simplifies sampling implementation, it may not fully support high-bandwidth controllers based on time-scale separation. The reduced bandwidth due to lowered sampling frequency will be highly improved through state-feedforward, which will be introduced in the following chapter.

III-C Flying Capacitor Voltage Estimator

III-C1 Multi-Cost Gradient Descent Method for Closed-Loop Estimation

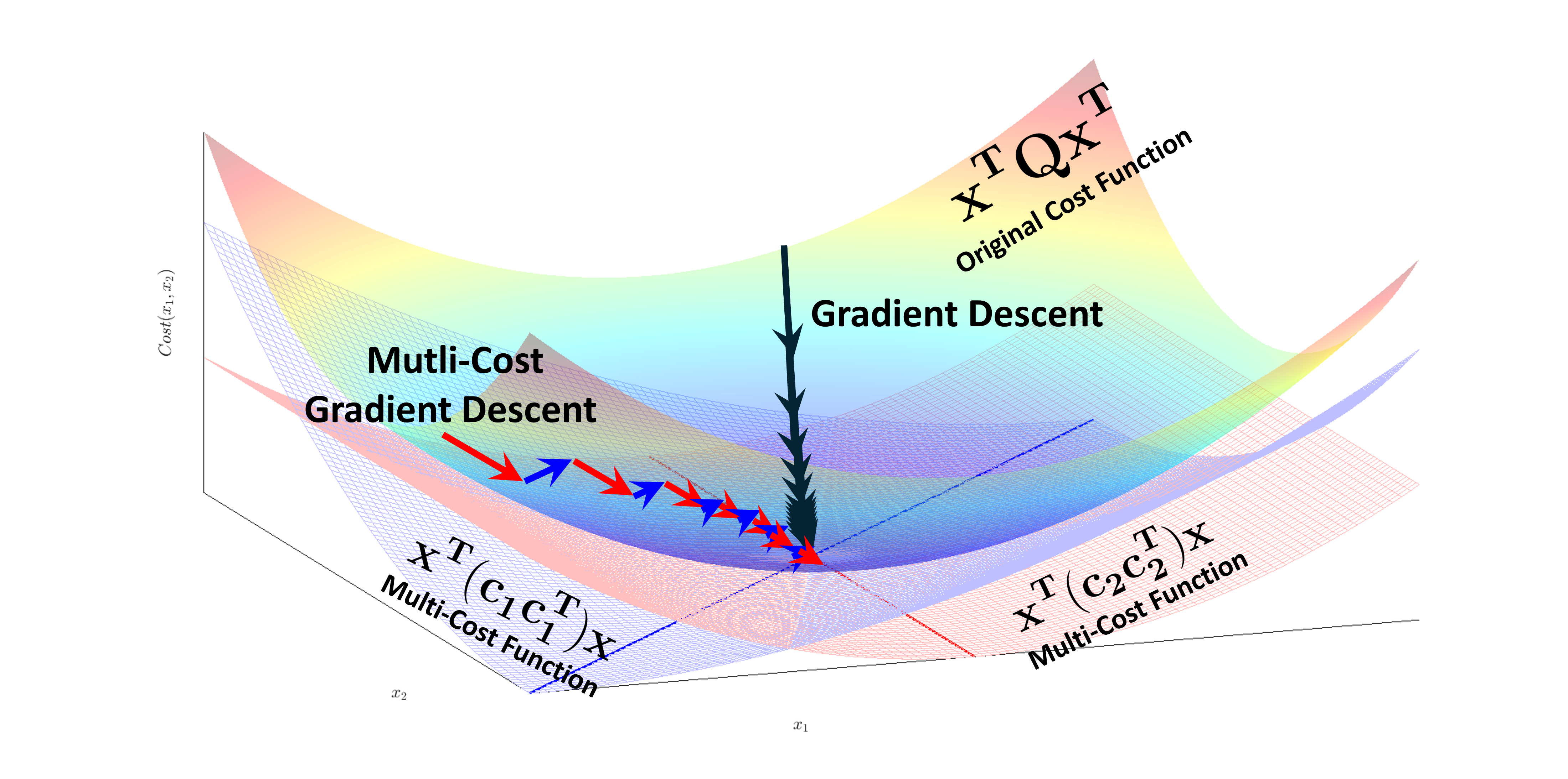

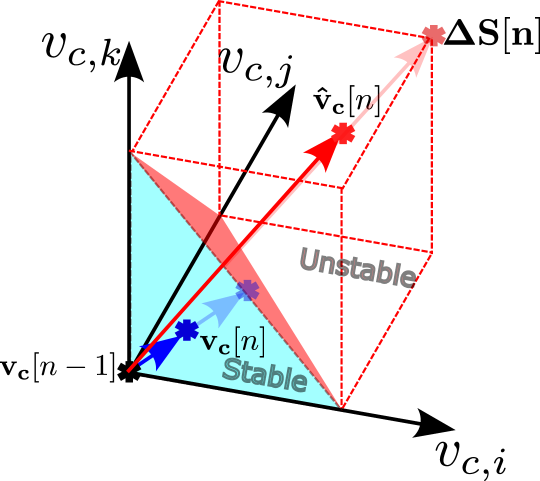

From an optimization perspective, the convex optimization problem for estimating flying capacitor voltages can be formulated as follows:

| (32) |

where , and denotes the estimated value of of closed-loop estimator. Here, ‘’ means matrix is positive definite. The optimal value is 0, and the optimal solution is .

Instead of solving the original optimization problem defined in (32), the proposed method proposes a multi-cost function approach shown in Fig. 7, defined as follows:

| (33) |

where ensures that each cost function is convex. The gradient descent method guarantees convergence to the optimal value, 0. The optimal condition is expressed as:

| (34) |

The intersection of solution is and the optimal solution is 0, which is same as the original optimization problem in (32), only if the following matrix is invertible (observability requirement):

| (35) |

This requires that:

| (36) |

For the proposed real-time estimation of flying capacitor voltages, the multi-cost gradient vectors are utilized. The closed-loop update function, based on the gradient descent method in the discrete-time domain (), is expressed as follows:

| (37) | ||||

where and denotes the identity matrix and feedback gain (learning rate). In (37), utilizing the pole voltage equation:

| (38) |

for setting the gradient vector , the update function becomes:

| (39) | ||||

where is learning rate, which is feedback gain. This update function links the flying capacitor voltage estimation to pole voltage () and input voltage (). By utilizing the switching state vector (), the gradient descent method can be effectively adapted to the physical characteristics of the FCML converter.

III-C2 State-Feedforward for Open-Loop Estimation

To enhance the dynamic response of the closed-loop estimator, an open-loop estimator is utilized for a state-feedforward.

According to dynamics of flying capacitor voltage () in (15), the flying capacitors are charged and discharged by inductor current () based on the switching state ().

Over one sampling period, the change in charge of each flying capacitor is determined by the product of and . can be estimated by the previous information of duty reference with deadtime, therefore the flying capacitor voltage can be estimated in open-loop as follows:

| (40) |

where denotes the estimated value of of open-loop estimator.

III-D Hybrid Estimator

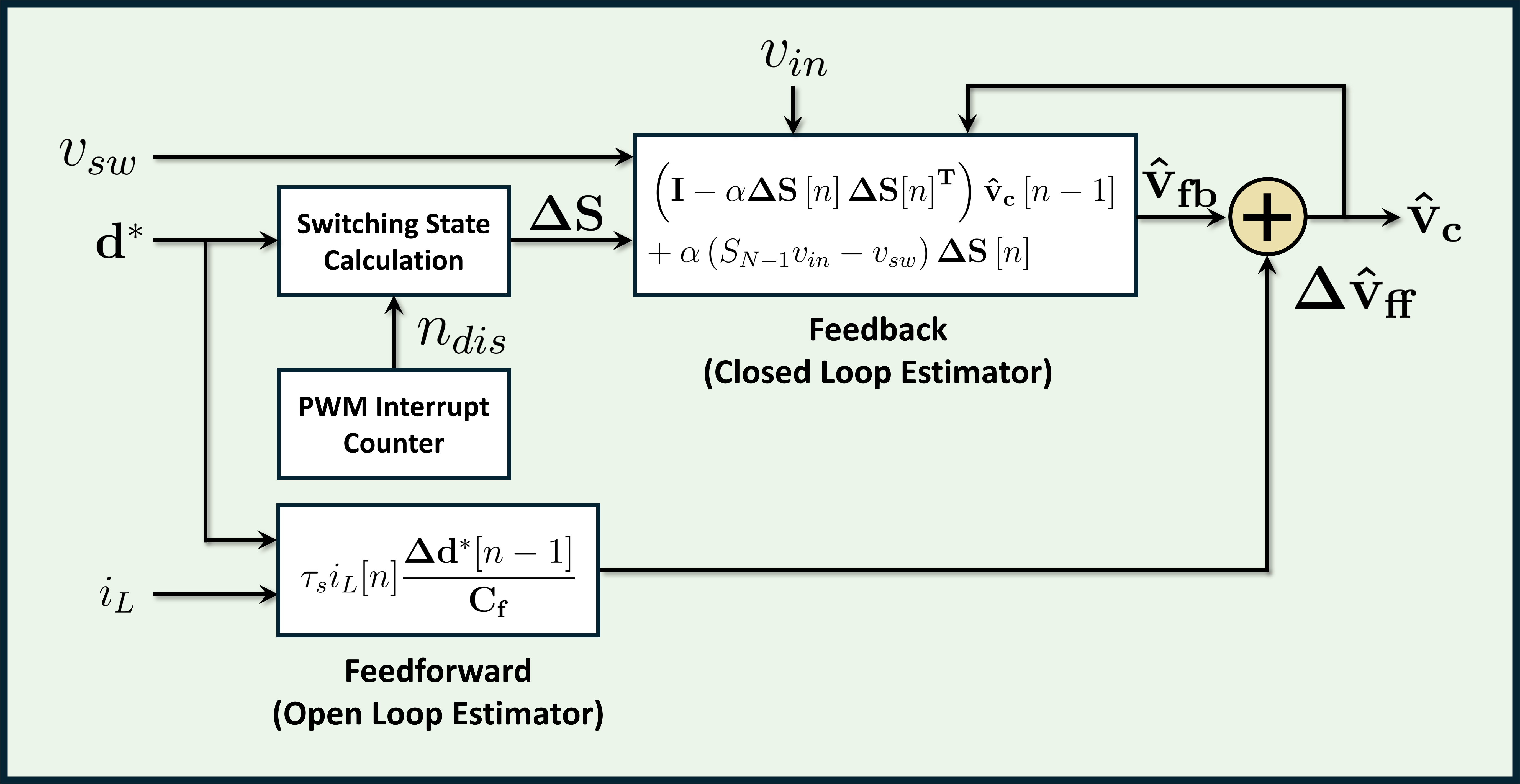

By integrating the closed-loop and open-loop estimators, the final update function is derived as follows:

| (41) |

| (42) | ||||

| (43) |

where , , and are the estimated flying capacitor voltage, the feedback and feedforward terms of hybrid estimator, respectively. The block diagram of the hybrid estimator is depicted in Fig. 8.

The feedback term ensures convergence to actual value of the estimated values under steady-state conditions while guaranteeing stability of the estimator. The feedforward term compensates the limited dynamic response of the closed-loop estimator caused by lower sampling and control frequency by utilizing the fast dynamic of the open-loop estimation.

The hybrid estimator combines the strengths of both methods, enabling rapid tracking of flying capacitor voltage changes with open-loop estimation, while ensuring stability and convergence with closed-loop estimation. This approach allows for achieving high-bandwidth performance even with low sampling and control rates, making high-bandwidth estimator-based control feasible with low-cost MCU.

The mathematical analysis of the proposed hybrid estimator, including its stability and proper gain setting, will be addressed in detail in the following chapter.

III-E Stability Analysis

(41) can be expressed in different way to analyze the stability in discrete-time domain as follows:

| (44) | ||||

Here, stability of the estimator is determined by the system matrix’s eigenvalues. The system matrix is

| (45) |

Here, both and are commutative and simultaneously diagonalizable, so the eigenvalues of system matrix are linear combinations of each matrix’s eigenvalues. Each non-zero row vector of is all paralleled each other and have a same magnitude with and the rank of is 1. Therefore, the eigenvalues of are 0 and . As a result, the eigenvalues of system matrix are

| (46) |

To make sure the stability of the estimator, all eigenvalues should be in a range between -1 and 1, in other words, , therefore the following inequation should be met:

| (47) |

III-F Frequency Response Characteristics

(44) can be expressed as follows:

| (49) | ||||

The feedback gain matrix in this formula is

| (50) |

which varies at every sampling instants. If the sampling frequency is significantly higher than the estimator’s bandwidth, the discrete-time update function in (49) can be approximated in continuous-time domain. The equivalent representation in continuous-time domain is expressed as follows:

| (51) |

Here, the proposed estimator contains variable proportional gain term, , and feedforward term. The laplace transform of (51) is as follows:

| (52) |

where

| (53) |

| (54) |

Then, (52) can be expressed with following forms:

| (55) |

| (56) |

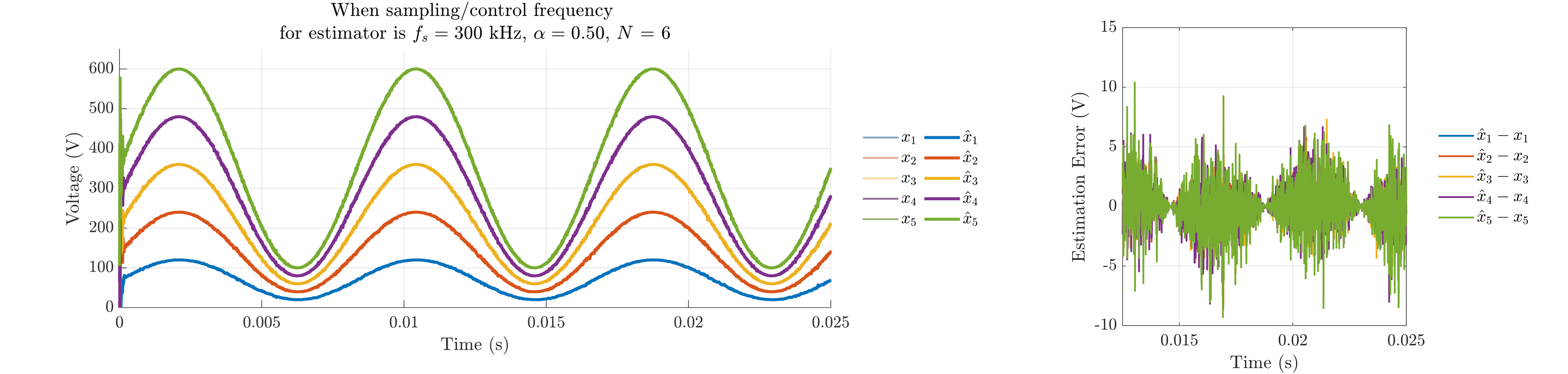

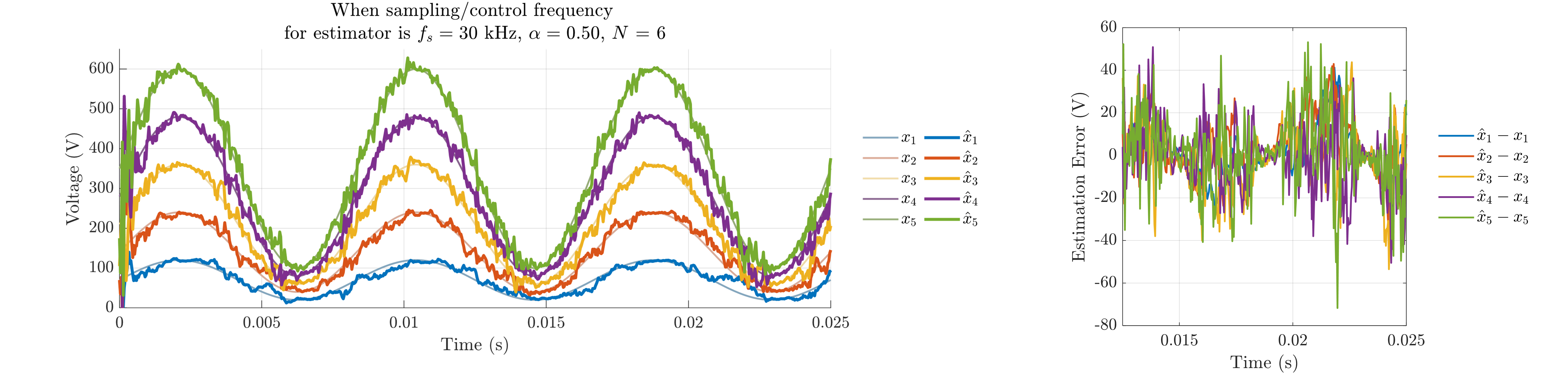

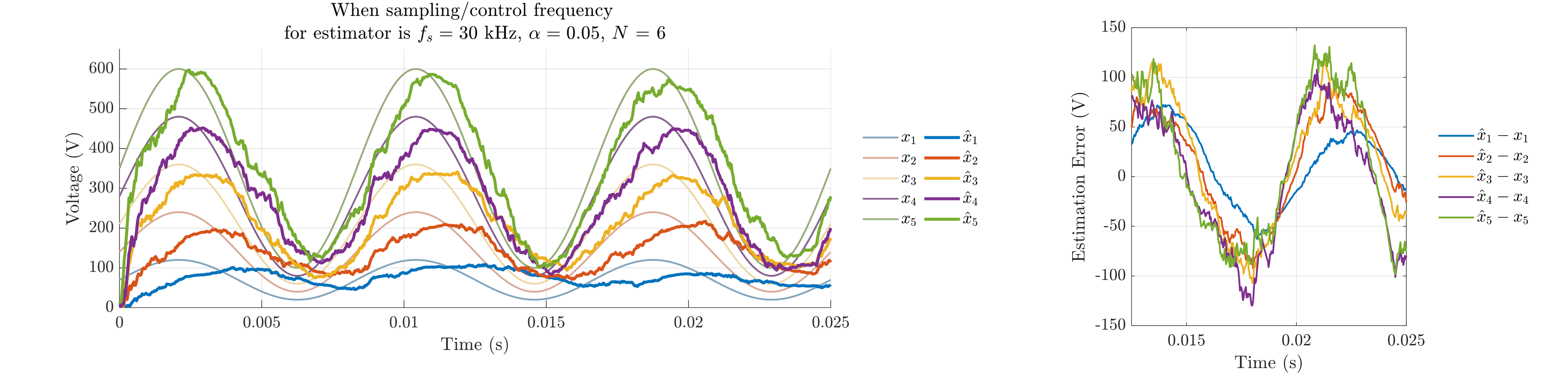

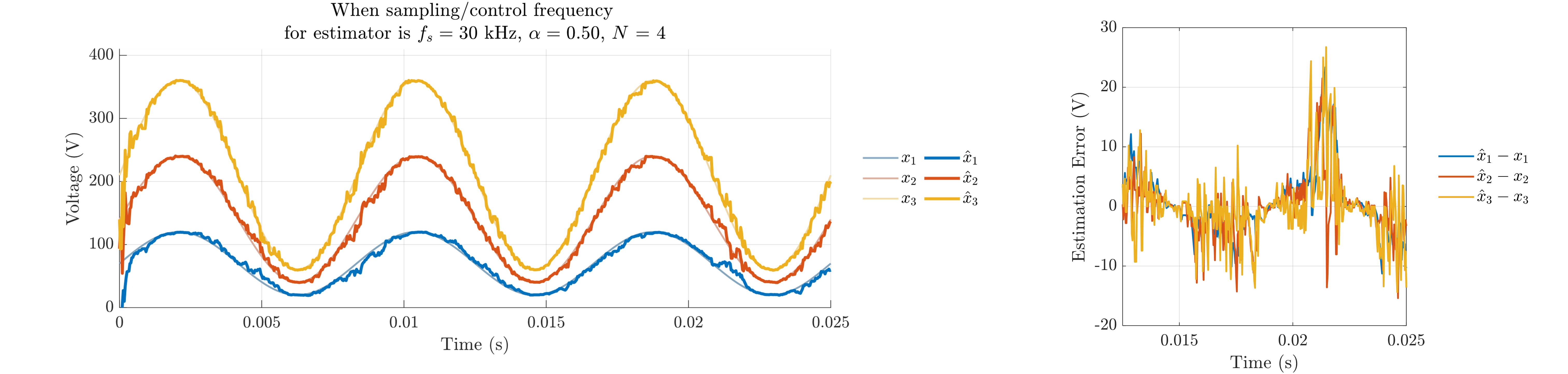

Fig. 10 shows the closed-loop estimation performance according to the FCML level (), feedback gain (), and sampling/control frequency (). In Fig. 10(a), when is high at 300 kHz, the estimation error is small. However, Fig. 10(b) shows the estimation error increases significantly when is reduced to 30 kHz. This error includes both high-frequency errors at the sampling frequency and errors in the fundamental frequency (120 Hz). As shown in Fig. 10(c) the feedback gain () is reduced to 0.05 compared to Fig. 10(b), leading to a lower bandwidth and significantly degraded estimation performance for the 120 Hz signal. Here, the estimation delay increases as bandwidth lowered. Conversely, the high-frequency error at the sampling frequency is decreased in Fig. 10(c) compared to Fig. 10(b) due to lowered . Interestingly, when the FCML level () is reduced to 4, decreasing the number of variables to estimate to 3, the estimation error is significantly lowered in Fig. 10(d) compared to the case in Fig. 10(b), even with the same feedback gain and sampling frequency. This is because a lower requires fewer to satisfy full-rank operation, reducing the impact of the single-rank of the multi-cost matrix on estimation error.

In summary, the closed-loop estimation performance degrades significantly with lower sampling frequency and higher FCML level. While increasing improves the estimation bandwidth, it also increases the high-frequency error caused by the single-rank of the multi-cost matrix at the sampling frequency level.

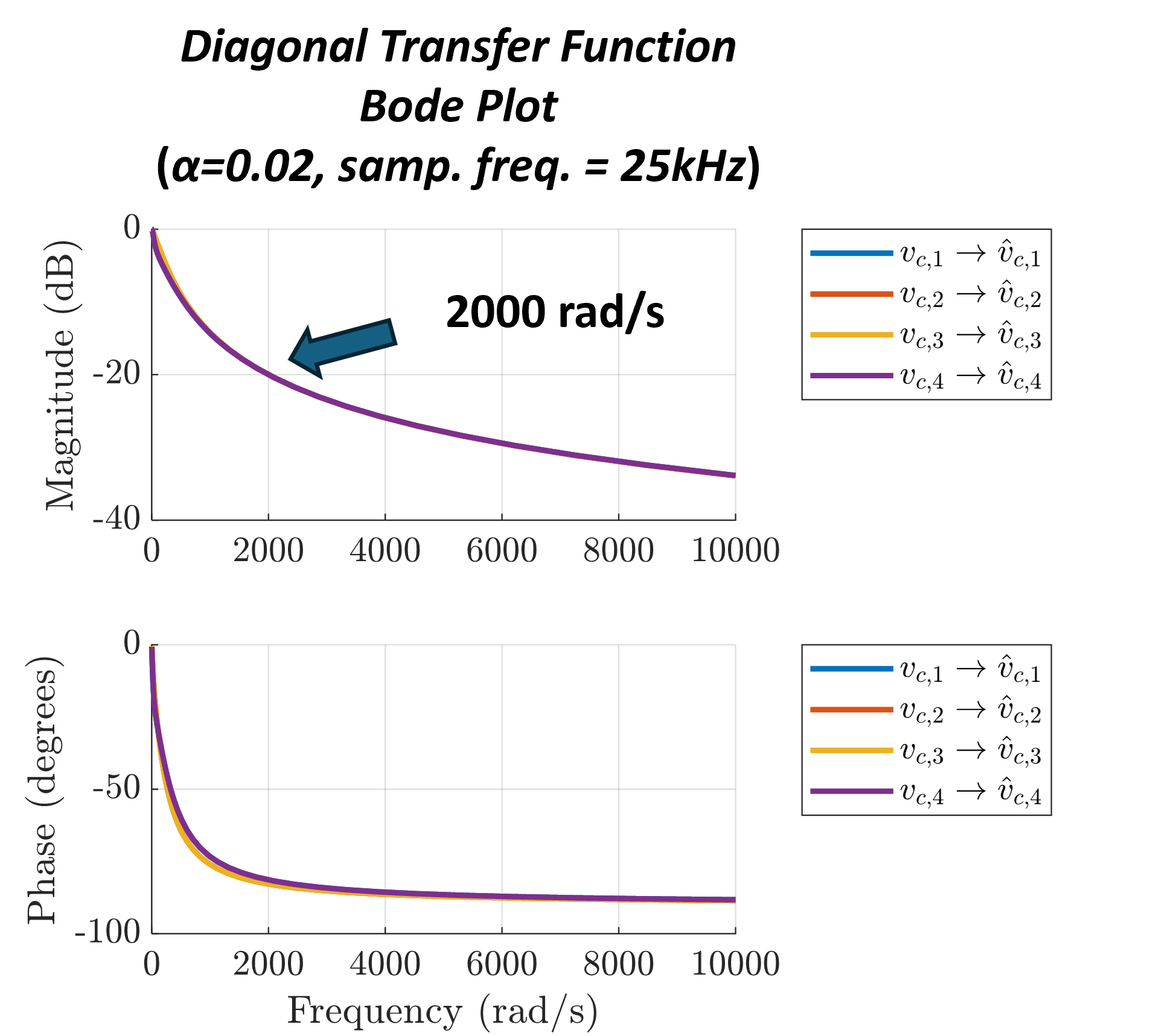

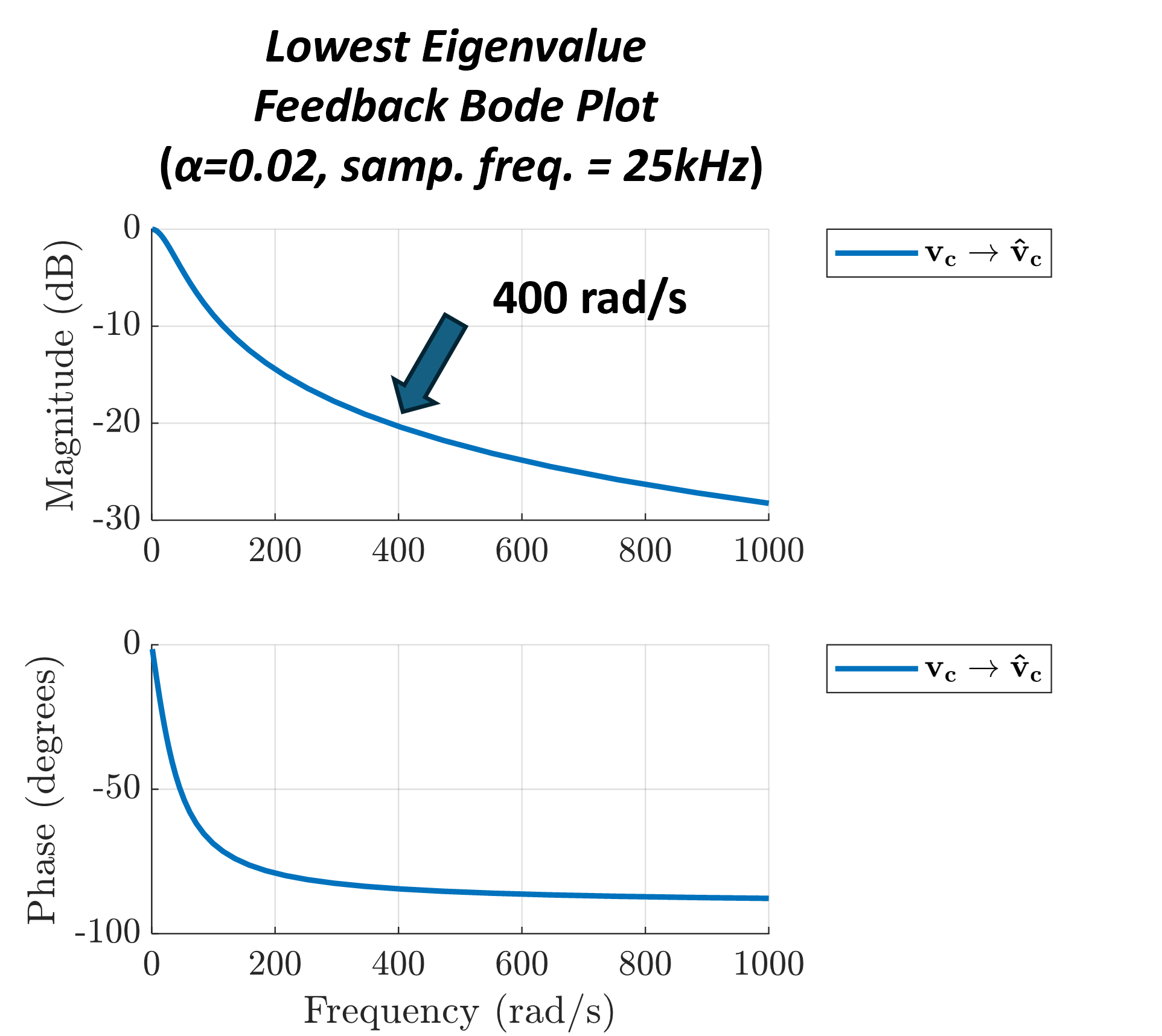

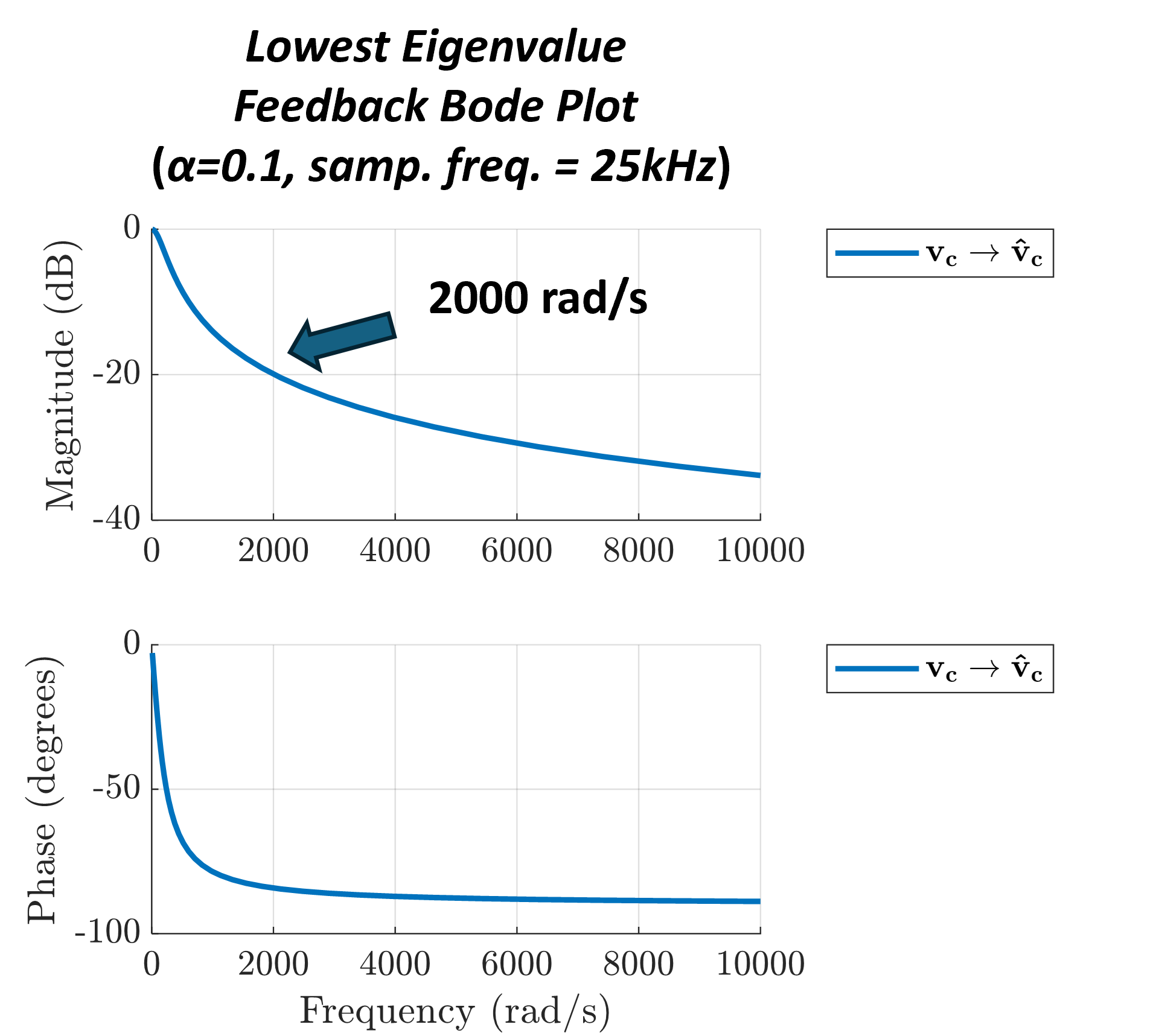

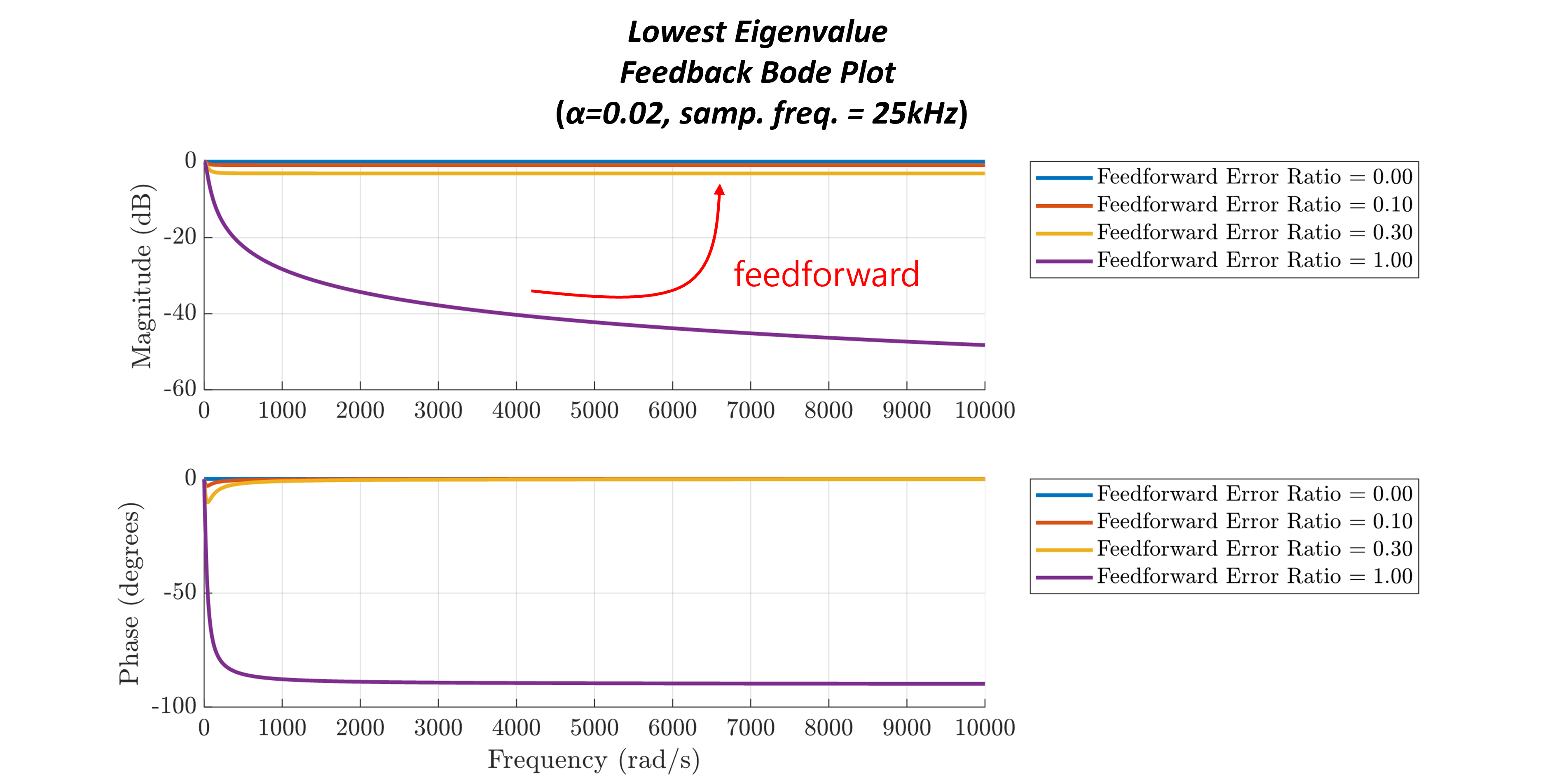

As shown in Fig. 11, the feedback term in the estimator acts as a low-pass filter as discussed in (56). It is important to note that Fig. 11 utilizes the diagonal transfer function, while the actual frequency response has a much lower bandwidth shown in Fig. 11. This is because, in a MIMO system, the bandwidth is determined by the lowest eigenvalue of the system matrix which cannot be shown in diagonal terms. A Bode plot of the transfer function, conservatively defined by the lowest eigenvalue, is shown in Fig. 12. It reveals that as increases, the bandwidth also increases, but remains significantly lower than that of the diagonal transfer function in Fig. 11.

On the other hand, the feedforward term in (56), derived from the open-loop estimation, behaves as a high-pass filter, estimating high-frequency components and rapid variations.

If the parameter error is zero and sampled inductor current and applied duty is same with actual values in ideal case, then, following equality holds:

| (57) |

therefore,

| (58) |

which shows that the estimated value is exactly same with the actual value, without any estimation delay and estimation errors. The Bode plot of the hybrid estimator with feedforward is shown in Fig. 13. This shows the performance of the hybrid estimator with fast dynamics. However, in real world, the parameter/sampling error can occur, which generates the feedforward term has some error. Despite minor errors in feedforward term, Fig. 13 shows the the feedforward term enhances the estimator’s performance.

In summary, the proposed hybrid estimator separates estimation tasks: low-frequency components are handled by closed-loop feedback, while high-frequency dynamics are managed by an open-loop feedforward path. The feedforward’s high-pass filtering characteristic prevents integrator wind-up by rejecting DC errors and allowing only high-frequency dynamics. This design achieves high bandwidth without requiring excessively high sampling rates, simplifying implementation while maintaining strong dynamic performance. In contrast, conventional feedback-only methods act as low-pass filters and require a high feedback gain () to minimize delay. The impact of feedforward errors, dependent on the choice of , will be discussed in the next chapter.

III-G Gain Setting

The proposed estimator employs an effective feedback gain matrix, , as defined in (50), which varies with the switching states. Furthermore, the feedback matrix depends on the FCML level and the combinations of duty cycle references. Due to this variability, must be configured to account for the worst-case scenarios, averaged over sampling instants, as illustrated in Fig. 12. If the FCML level and operating conditions are constrained, the gain can be adjusted more flexibly, enabling improved performance under specific conditions.

III-G1 Upper Bound, High Frequency Error from Instantaneous Rank Deficiency

The proposed estimator utilizes a multi-cost gradient descent approach because the exact gradient of the cost function in (32) cannot be directly obtained under the given conditions. However, it entails estimation errors oscillating at the sampling frequency as shown in Fig. 10. These errors arise from discrepancies between the actual gradient of the cost function and the switching state vector, caused by a single rank of system matrix at each time instant.

To mitigate the high-frequency estimation error from the feedback term, the feedback gain () must be carefully selected. A high accelerates the feedback response but amplifies high frequency errors, potentially introducing disturbances in both current control and active voltage balancing.

The variation in the estimated value () updated by the feedback term must be controlled to reduce excessive high-frequency noise. To achieve this, assuming that the estimation error at is zero, the following inequality can be applied:

| (61) | ||||

where is the allowable maximum high-frequency error from feedback term. The upper bound of can be set as follows:

| (62) |

As the sampling period () decreases, indicating higher sampling and control frequencies, the upper bound of in (62) increases. This tendancy can be found in Fig. 10. This is because the voltage difference of the input voltage is reduced with faster sampling. Conversely, as the level of the FCML increases, the upper bound decreases. This occurs because the dimension of the vector space for flying capacitor voltages grows with higher levels, requiring more sampling instances () to achieve full-rank operation.

In summary, the instantaneous rank deficiency of the multi-cost matrix introduces high frequency errors during a single update. These errors become more significant as the FCML level increases, given that achieving full-rank operation requires dimensions.

III-G2 Lower Bound, Step 1: Eigenvalues of the System Matrix

The matrix

| (63) |

contains the eigenvectors of each system matrix . For ensuring observability, the matrix must achieve full rank ().

Meanwhile, the eigenvalues of the product matrix are given as:

| (64) |

The eigenvectors/eigenspace and eigenvalues of each individual system matrix () are defined as:

| (65) |

| (66) |

, respectively. Here, the eigenvalue has degeneration. All eigenvalues of lie within the range according to (64), (66).

However, for the product matrix , all eigenvalues lie strictly within the range . If an eigenvalue of equaled , the following condition must have held:

| (67) |

This condition implies that the eigenvector , corresponding to the eigenvalue , resides in the orthogonal complement of the span of , according to (63) and (65). However, since has full rank, the span fully covers . Consequently, no eigenvector exists that satisfies this condition. Therefore, all eigenvalues of are strictly confined to the range .

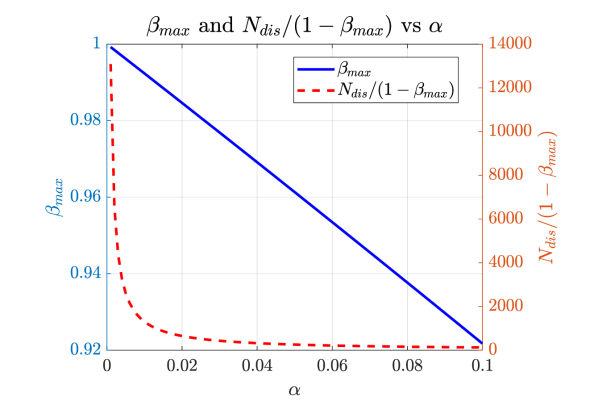

The maximum eigenvalue of can be expressed as:

| (68) |

As increases, decreases strictly as shown in Fig. 14. This behavior shows the influence of on the eigenvalue spectrum of . A higher value of results in a lower , leading to faster convergence of the estimator.

III-G3 Lower Bound, Step 2. The Effect of Parameter and Sampling Error

For simpicity, the extra term except for the estimation error component, , can be expressed with as follows:

| (69) | ||||

Then (44) can be simplified as follows:

| (70) |

With this, the estimation error is calculated as follows:

| (71) |

The upper bound of DC-error in steady state condition is calculated as follows:

| (72) | ||||

As discussed before, is strictly decreased as increased, meaning that as increases, the DC-offset error in the estimation value from the feedforward error () increases, which implies that must be sufficiently large to minimize the DC-offset error. Accordingly, the lower bound of is derived as follows:

| (73) |

where is a decreasing function as shown in Fig. 14, and is allowable maximum DC estimation error. As the FCML level () increases, also rises according to (29), leading to a higher lower bound for to maintain the same DC offset error. This is caused by the instantaneous rank-deficiency of the system matrix ().

A larger feedback gain () reduces the DC offset error caused by feedforward inaccuracies. However, as increases, the rank-deficiency effect becomes more severe, further raising the minimum required . Conversely, higher sampling frequencies (shorter sampling periods) alleviate this problem by resolving rank-deficiency more quickly.

III-G4 Summary of Gain Setting

Both the upper and lower bounds for are influenced by the FCML level () and the sampling frequency. Higher and lower sampling frequencies increase the difficulty of selecting an appropriate gain due to amplified high-frequency and DC errors, which stem from the rank-deficiency effects of the multi-cost gradient descent method.

III-H Prolonged Rank-Deficiency Problem

In certain scenarios, prolonged rank-deficiency problem can happen. This situation may cause the estimated value to diverge due to feedforward errors or oscillate without any updates in null-space of from the feedback term.

III-H1 Switching Noise at Sampling Instants

During switching transitions, factors such as parasitic inductance in current commutation path, the rising/falling time caused by the gate-source capacitor’s charging/discharging through the gate driver, and PWM signal delays can prevent the pole voltage from settling at the sampling instants. Consequently, the unsettled pole voltage may be sampled instead. This results in distorted estimation through feedback term. This issue becomes particularly significant in DC-DC conversion cases where the duty cycle () does not inherently change in steady state.

The duty cycle at which switching and sampling can coincide () is calculated as follows:

| (74) |

For , is depicted in Fig. 15. The duty cycles near can be also influenced by unsettled pole voltage. As a result, the proposed method has limitations in accurately estimating voltages due to unsettled pole voltage, as switching effects distort the sampling and feedback estimation. In such case, two methods can be considered to avoid the problem.

First, dithering in the duty cycle reference can be used to avoid the unsettled pole voltage at sampling instants [24]. However, this dithering introduces additional ripples in the inductor current and flying capacitor voltage due to changes in the effective pole voltage, which can also affect to their controllers. To address this, the controller can utilize anti-windup to eliminate the additionally induced current and voltage by the dithering.

| N (Level of FCML) | Full-Rank? | |

| 3 | 1 | |

| 4 | 1 | |

| 5 | 0 | |

| 6 | 0.2 | |

| 0 |

Secondly, by modifying the PWM method, the effective pole voltage can be maintained while preventing the switching instant and sampling instant from occurring simultaneously. By employing the skipped adjacency PWM (SAPWM) in [31], the duty references can avoid the problematic region. However, this method requires additional external digital circuit and has the drawback of doubling the volt-second, leading to increase in switching ripple on inductor current and flying capacitor voltage.

In AC-DC buck operation, the periodic variation of the input voltage in steady state causes continuous changes in the required duty cycle, resulting in temporary rank-deficiency during specific time intervals. When rank-deficiency occurs due to switching effects, can be temporarily set to zero, relying entirely on the feedforward term for estimation. This approach is more effective than using dithering or SAPWM, which introduce additional switching ripple. By temporarily utilizing the feedforward term, the rank-deficiency issue caused by switching effects can be effectively addressed, particularly in AC-DC buck operation.

III-H2 Insufficiency of Disjoint Sampling For Full-Rank Operation

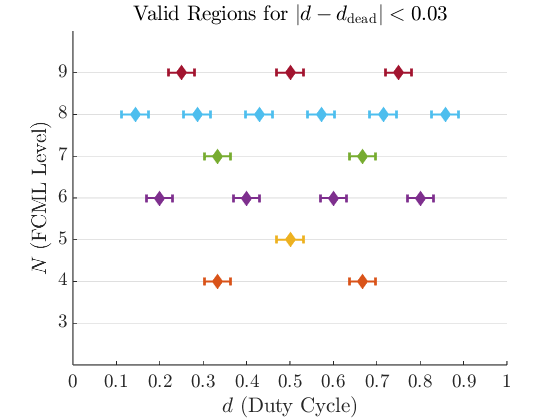

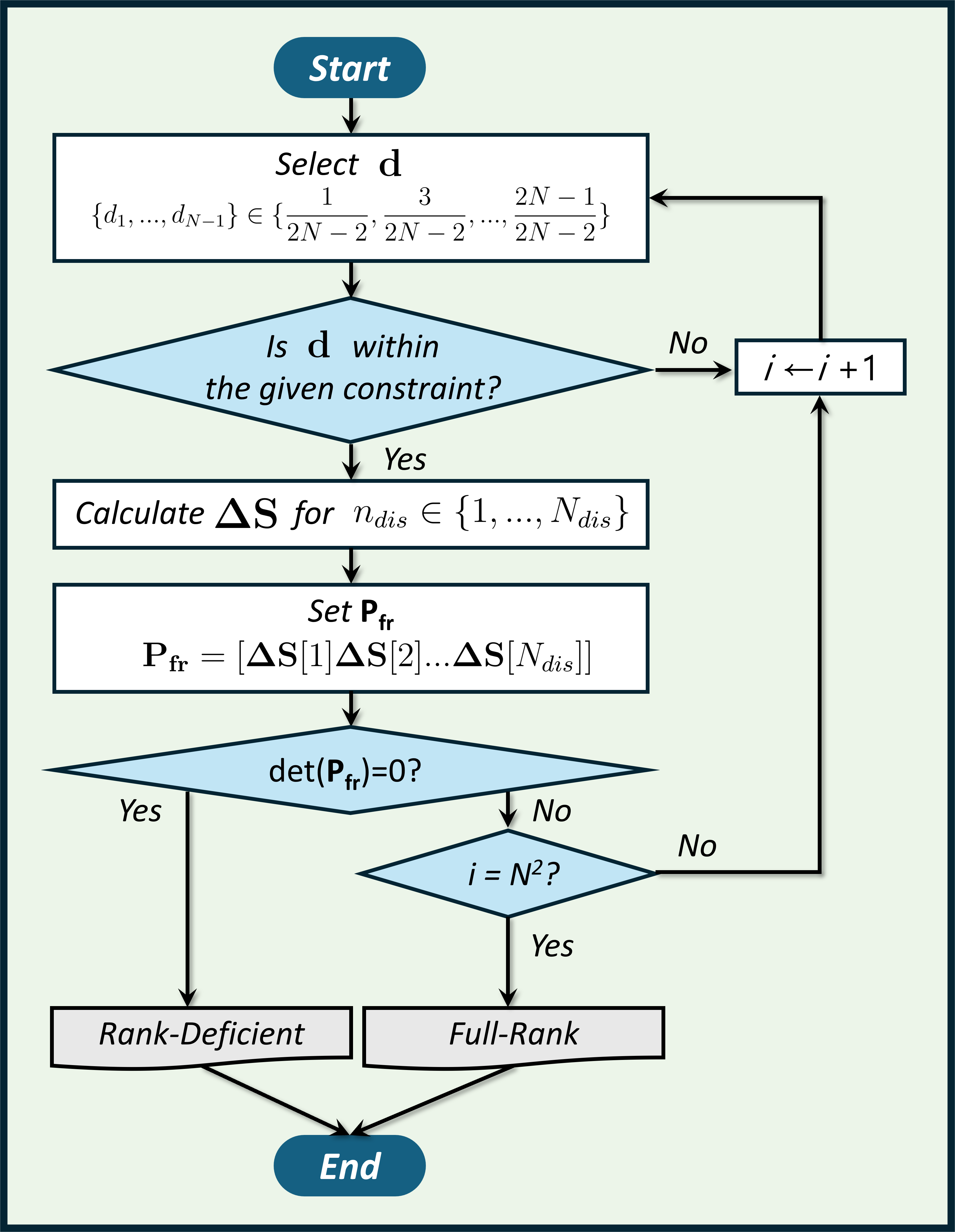

The proposed method relies on disjoint sampling for the pole voltage, requiring the switching state vectors to achieve full-rank operation across sampling instants. However, where active balancing is essential, the duty cycle references applied to each switch can differ, and the degree of freedom in duty combination increases with the FCML level (). Consequently, it is necessary to evaluate whether the disjoint sampling is applicable for full-rank operation across the duty cycle combinations.

Using the algorithm diagram provided in Fig. 16, the full-rank operation was iteratively verified in MATLAB for all duty cycle vectors. The result in TABLE II reveals that for , the disjoint sampling does not guarantee full-rank operation. Specifically, during the samplings, where peak/valley sampling of the PSPWM carrier is used, the set of the switching state vectors fail to satisfy full-rank operation for all duty cycle combinations. Therefore, the proposed method can only be applied universally to FCMLs with or .

However, in practical scenarios, is typically limited as discussed in (18) to small values (e.g. 0.05) to limit the impact of active balancing controller on the current controller. These constraints restrict the duty cycle references generated by the active voltage balancing controller. When is limited to 0.2 or less, full-rank operation becomes feasible even for . As a note, in the case of , it is difficult to achieve a full rank operation through disjoint sampling compared to because the peak and valley points of the PSPWM carriers overlap as shown in Fig. 5.

In summary, the proposed method is applicable to FCMLs with , , and . 6-level FCML is particularly relevant in cases where estimator-based control is required for active balancing, especially in AC-DC buck operations. Notably, the constrained output of active balancing controller enables full-rank operation for , making it suitable for grid-connected AC-DC buck converters employing 100 V GaN devices. This highlights the potential for data center applications, allowing low-cost CPUs to implement estimator-based control for 6-level FCML AC-DC buck conversion.

Furthermore, to extend the applicability of the proposed method, additional voltage sensors can be employed to relax the full-rank condition. This enables full-rank operation for FCML with other levels or . The placement of these voltage sensors should be optimized to effectively ensure full-rank operation, providing an efficient solution in terms of hardware design.

IV Results

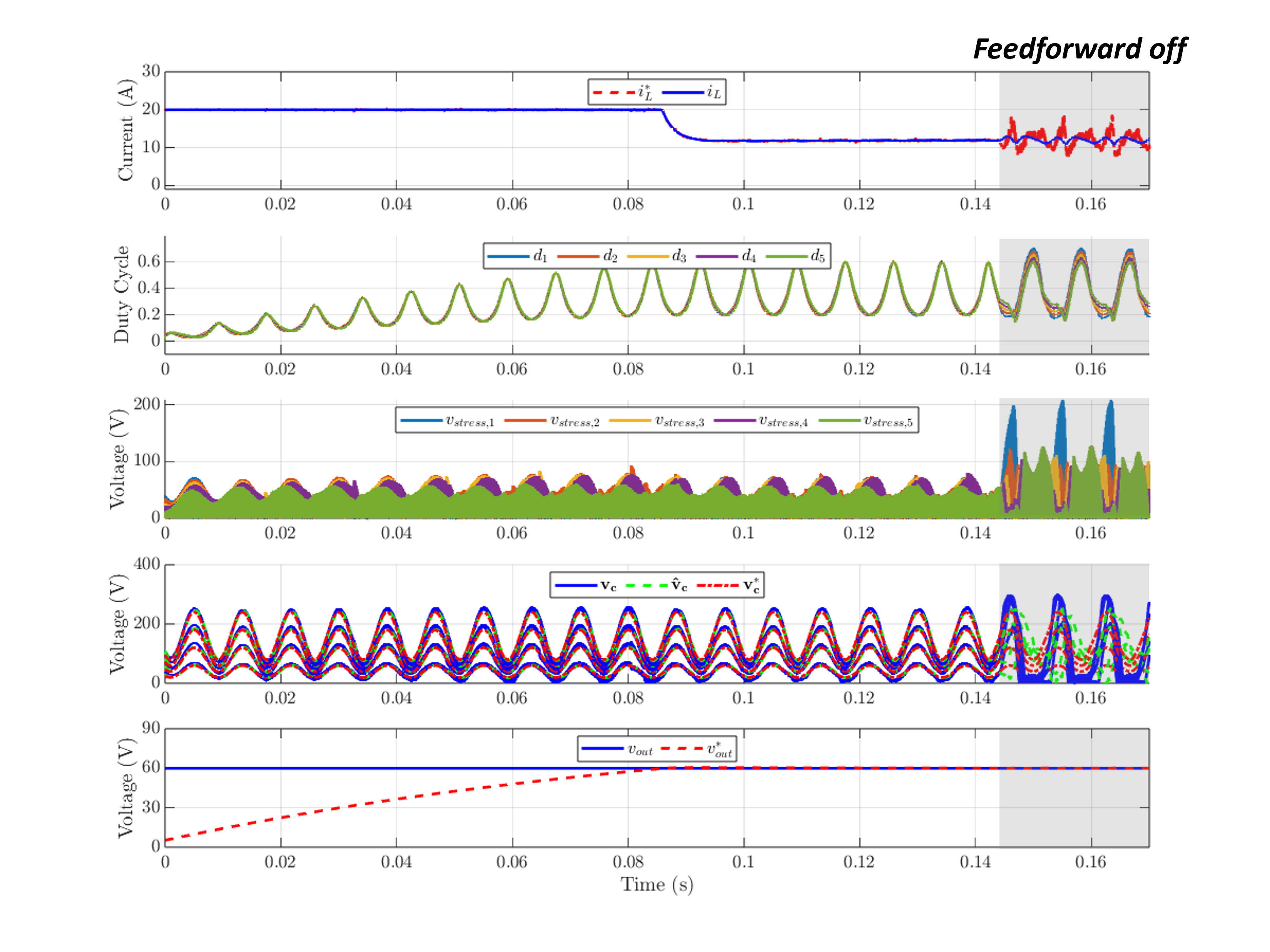

Fig. 18 presents the simulation results of the estimator-based control system, including output voltage control, active voltage balancing, and current control. The cascaded control system, as shown in Fig. 17, is designed with time-scale separation to ensure non-interference among controllers. The FCML parameters and controller bandwidths are listed in TABLE III. The simulation verifies the high-bandwidth characteristics of the proposed estimator by demonstrating DC current control for output voltage regulation under a varying input voltage of 120 Hz. The sampling frequency is approximately 25 kHz, suitable for low-cost MCUs.

During s, the output voltage is controlled from 0 V to 60 V, with the current reference limited to 20 A. The estimated flying capacitor voltage closely tracks the actual value, ensuring effective active voltage balancing. This prevents overvoltage, maintaining voltage stress on all switching devices below 100 V. As the output voltage increases, the required duty cycle also rises. Full-rank operation is maintained under the duty difference constraint, ensuring accurate estimation throughout the simulation. After the output voltage reaches the reference value, the current reference is reduced to match the load current without integrator wind-up issue, maintaining the output voltage.

After s, the feedforward input is disabled to see the importance of state feedforward, leaving the estimator to rely solely on feedback. Due to the combination of low , a high FCML level (), and a low sampling frequency, the feedback estimation significantly degrades, increasing estimation errors. This leads to poor current control and active voltage balancing, resulting in excessive voltage stress on switching devices, reaching nearly 200 V at maximum. Such overvoltage may lead to failure in 100 V-rated switching devices. The results highlight the importance of feedforward input and proper bandwidth settings for maintaining stable operation of all controllers. The result of the proposed method shows its superiority by enabling high-bandwidth estimator-based control even at low sampling rates. This highlights the effectiveness and practicality of the estimator in achieving robust control performance with reduced computational and sampling requirements.

| Parameter | Value |

|---|---|

| FCML Level () | 6 |

| Switching frequency () | 120 kHz |

| Effective switching frequency () | 600 kHz |

| Sampling frequency () | 25.53 kHz () |

| Output voltage reference () | 60 V |

| Input voltage frequency () | 120 Hz |

| Inductor () | 100 H |

| Output capacitor () | 20 mF |

| Flying capacitor () | 2.2 F |

| Current Controller Bandwidth | 3000 Hz |

| Voltage Controller Bandwidth | 45 Hz |

| Active Balancing Controller Bandwidth | 246 Hz |

| Feedback gain () | 0.047 |

| Load resistance () | 5 |

V Conclusion

This article proposes an estimator-based control framework for hybrid FCML converters, addressing limitations of conventional approaches with a hybrid estimation method that combines high-bandwidth closed-loop feedback and rapid open-loop feedforward dynamics. The proposed approach eliminates reliance on isolated voltage sensors by utilizing high-bandwidth flying capacitor voltage estimation. Key contributions include a detailed analysis of stability and gain tuning, and the effects of rank-deficiency. The methodology is proposed to achieve high-bandwidth active voltage balancing and current control with reduced sampling rates, offering a practical and scalable solution for power electronics applications for grid-tied datacenters, electric aircraft, and motor drive.

References

- [1] T. Meynard and H. Foch, “Multi-level conversion: high voltage choppers and voltage-source inverters,” in PESC ’92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, 1992, pp. 397–403 vol.1.

- [2] J.-S. Lai and F. Z. Peng, “Multilevel converters—a new breed of power converters,” in Proc. IEEE 30th Conf. Rec. Ind. Appl. Conf., vol. 3, Oct. 1995, pp. 2348–2356.

- [3] A. Radi, S. M. Ahsansuzzaman, B. Mahdavikhah, and A. Prodic, “High-power density hybrid converter topologies for low-power dc-dc smps,” in Proc. Int. Power Electron. Conf., May. 2014, pp. 3582–3586.

- [4] Y. L. A. Stillwell and R. C. N. Pilawa-Podgurski, “A method to extract low-voltage auxiliary power from a flying capacitor multilevel converter,” in Proc. IEEE 17th Workshop Control Modeling Power Electron., Jun. 2016, pp. 1–8.

- [5] W. L. Y. Lei and R. C. N. Pilawa-Podgurski, “An analytical method to evaluate and design hybrid switched-capacitor and multilevel converters,” IEEE Transactions on Power Electronics, vol. 33, no. 3, pp. 2227–2240, 2018.

- [6] S. Qin, Y. Lei, I. Moon, C. Haken, E. Bian, E. Saathoff, W. Chung, D. Chou, and R. C. Pilawa-Podgurski, “A high power density power factor correction front end based on a 7-level flying capacitor multilevel converter,” in 2016 IEEE 2nd Annual Southern Power Electronics Conference (SPEC), 2016, pp. 1–6.

- [7] Z. Ye, Y. Lei, W.-C. Liu, P. S. Shenoy, and R. Pilawa-Podgurski, “Improved bootstrap methods for powering floating gate drivers of flying capacitor multilevel converters and hybrid switched-capacitor converters,” IEEE Transactions on Power Electronics, vol. 35, no. 6, pp. 5965–5977, 2020.

- [8] S. Coday, A. Barchowsky, and R. C. Pilawa-Podgurski, “A 10-level gan-based flying capacitor multilevel boost converter for radiation-hardened operation in space applications,” in 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), 2021, pp. 2798–2803.

- [9] N. Pallo, T. Foulkes, T. Modder, S. Coday, and R. Pilawa-Podgurski, “Power-dense multilevel inverter module using interleaved gan-based phases for electric aircraft propulsion,” in 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2018, pp. 1656–1661.

- [10] A. Lidow, A. Nakata, M. Rearwin, J. Strydom, and A. M. Zafrani, “Single-event and radiation effect on enhancement mode gallium nitride fets,” in 2014 IEEE Radiation Effects Data Workshop (REDW), 2014, pp. 1–7.

- [11] R. S. Bayliss, R. K. Iyer, R. Liou, and R. C. Pilawa-Podgurski, “A segmented electric aircraft drivetrain employing 10-level flying capacitor multi-level dual- interleaved power modules,” in 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), 2023, pp. 225–230.

- [12] R. S. Bayliss and R. C. Pilawa-Podgurski, “An input inductor flying capacitor multilevel converter utilizing a combined power factor correcting and active voltage balancing control technique for buck-type ac/dc grid-tied applications,” in 2024 IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), 2024, pp. 1–7.

- [13] R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, “A combined power factor correcting and active voltage balancing control technique for buck-type ac/dc grid-tied flying capacitor multilevel converters,” in 2023 IEEE 24th Workshop on Control and Modeling for Power Electronics (COMPEL), 2023, pp. 1–5.

- [14] E. Candan, N. C. Brooks, A. Stillwell, R. A. Abramson, J. Strydom, and R. C. N. Pilawa-Podgurski, “A six-level flying capacitor multilevel converter for single-phase buck-type power factor correction,” IEEE Transactions on Power Electronics, vol. 37, no. 6, pp. 6335–6348, 2022.

- [15] A. Stillwell and R. C. N. Pilawa-Podgurski, “A five-level flying capacitor multilevel converter with integrated auxiliary power supply and start-up,” IEEE Transactions on Power Electronics, vol. 34, no. 3, pp. 2900–2913, 2019.

- [16] S. Coday, N. M. Ellis, and R. C. N. Pilawa-Podgurski, “Modeling and analysis of shutdown dynamics in flying capacitor multilevel converters,” IEEE Transactions on Power Electronics, vol. 39, no. 8, pp. 9150–9159, 2024.

- [17] J. S. R. Z. Xia, B. L. Dobbins and J. T. Stauth, “State space analysis of flying capacitor multilevel dc-dc converters for capacitor voltage estimation,” in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 50–57.

- [18] M. Khazraei, H. Sepahvand, K. Corzine, and M. Ferdowsi, “Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters,” IEEE Transactions on Industrial Electronics, vol. 59, no. 2, pp. 769–778, 2012.

- [19] G. Farivar, J. P. M. Y. Ghias, A. B. Hredzak, and V. G. Agelidis, “Capacitor voltages measurement and balancing in flying capacitor multilevel converters utilizing a single voltage sensor,” IEEE Transactions on Power Electronics, vol. 32, no. 10, pp. 8115–8123, 2017.

- [20] A. Stillwell, E. Candan, and R. C. N. Pilawa-Podgurski, “Active voltage balancing in flying capacitor multilevel converters with valley current detection and constant effective duty cycle control,” IEEE Transactions on Power Electronics, vol. 34, no. 11, pp. 4291–4411, 2019.

- [21] R. K. Iyer, I. Z. Petric, R. S. Bayliss, N. C. Brooks, and R. C. N. Pilawa-Podgurski, “A high-bandwidth parallel active balancing controller for current-controlled flying capacitor multilevel converters,” IEEE Transactions on Power Electronics, vol. 39, no. 10, pp. 12 951–12 965, 2024.

- [22] I. Hwang, Y.-C. Kwon, and S.-K. Sul, “Enhanced dynamic operation of heavily saturated ipmsm in signal-injection sensorless control with ancillary reference frame,” IEEE Transactions on Power Electronics, vol. 38, no. 5, pp. 5726–5741, 2023.

- [23] I. Hwang, J. Lee, and S. Cui, “Grid voltage sensorless control of 3.2kw bridgeless totem-pole pfc converter with pre-estimation and seamless mode-transition,” in 2024 IEEE Applied Power Electronics Conference and Exposition (APEC), 2024, pp. 1–5.

- [24] I. Z. Petric, R. K. Iyer, N. C. Brooks, and R. C. N. Pilawa-Podgurski, “A real-time estimator for capacitor voltages in the flying capacitor multilevel converter,” in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–8.

- [25] Z. Xia, B. L. Dobbins, J. S. Rentmeister, and J. T. Stauth, “State space analysis of flying capacitor multilevel dc-dc converters for capacitor voltage estimation,” in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC). IEEE, 2019, pp. 50–57.

- [26] S.-K. Sul, Control of Electric Machine Drive System. Piscataway, NJ: IEEE Press, 2011.

- [27] Y. L. A. Stillwell and R. C. N. Pilawa-Podgurski, “A 5-level flying capacitor multilevel converter with integrated auxiliary power supply and start-up,” Proc. IEEE Appl. Power Electron. Conf. Expo., pp. 2923–2938, Mar. 2017.

- [28] H. Khalil, “Nonlinear systems,” 2002.

- [29] I. C. Cosme, I. F. Fernandes, J. L. de Carvalho, and S. X. de Souza, “Memory-usage advantageous block recursive matrix inverse,” Applied Mathematics and Computation, vol. 328, pp. 125–136, 2018. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S0096300318300742

- [30] A. Krishnamoorthy and D. Menon, “Matrix inversion using cholesky decomposition,” in 2013 Signal Processing: Algorithms, Architectures, Arrangements, and Applications (SPA), 2013, pp. 70–72.

- [31] I. Hwang, “Skipped adjacency pulse width modulation: Zero voltage switching over full duty cycle range for hybrid flying capacitor multi-level converters without dynamic level changing,” 2024. [Online]. Available: https://arxiv.org/abs/2411.06589