Microwave Engineering for Semiconductor Quantum Dots in a cQED Architecture

Abstract

We develop an engineered microwave environment for coupling high Q superconducting resonators to quantum dots using a multilayer fabrication stack for the dot control wiring. Analytic and numerical models are presented to understand how parasitic capacitive coupling to the dot bias leads can result in microwave energy leakage and low resonator quality factors. We show that by controlling the characteristic impedance of the dot bias wiring, on-chip quality factors of can be attained without the addition of explicit filtering. Using this approach we demonstrate single electron occupation in double and triple dots detected via dipole or quadrupole coupling to a superconducting resonator. Additionally, by using multilayer fabrication we are able to improve ground plane integrity and keep microwave crosstalk below -20 dB out to 18 GHz while maintaining high wire density which will be necessary for future circuit quantum electrodyanmics (cQED) quantum dot processors.

Gate defined quantum dots are a nascent platform for quantum computing in which electron charge and spin states are used to define the quantum bitHanson et al. (2007); Zwanenburg et al. (2013). In silicon and Si/SiGe heterostructures, recent work has shown it is possible to fabricate single, two, and four qubit systemsYoneda et al. (2018); Veldhorst et al. (2015); Kawakami et al. (2016); Zajac et al. (2018); Sigillito et al. (2019); Mi et al. (2018); Watson et al. (2018) with control infidelities at or approaching the level requisite for error correctionFowler et al. (2012). For most quantum dot circuits, the control wiring scheme consists of an electron beam (e-beam) defined gate electrode structure with a rapid fan out into pads that are connected by aluminum or gold wire bonds to a printed circuit board (PCB) with typical die sizes of only a few millimeters. While this keeps the fabrication complexity to a minimum, it results in a minimally controlled microwave environment for the device and any readout circuitry. Near term quantum computing efforts with quantum dots face significant quantum systems engineering challenges balancing the needs for high fidelity readout, coupling, and control.

In this letter, we demonstrate a wiring scheme for quantum dot devices in a cQED architecture. This approach allows for high-density, low crosstalk wiring with controlled RF leakage characteristics, paving the way for larger quantum dot processors utilizing cQED techniques Mi et al. (2018); Stockklauser et al. (2017); Samkharadze et al. (2018). A simple and intuitive circuit model for cavity leakage from external leads reveals that minimization of the impedance of the environment at the cavity frequency ameliorates photon leakage out the gate leads, which otherwise present an undesired load on the cavity. We implement this method with a microstrip wiring scheme that achieves a low characteristic lead impedance of , and demonstrate resonators with quality factors as high as 8140 (design ) while connected to the quantum dot gate stack.

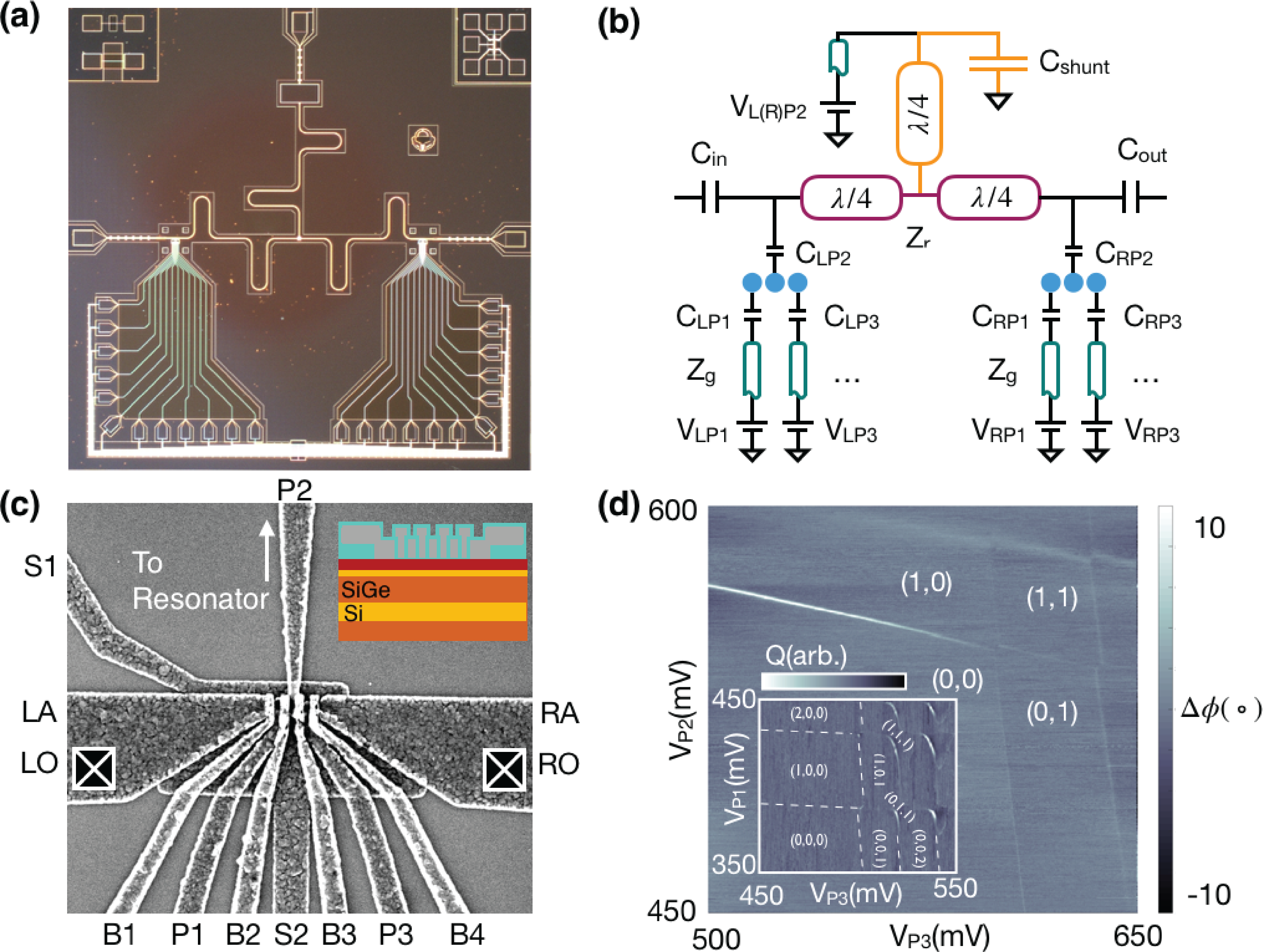

For these experiments, we fabricate cavity-coupled pairs of triple quantum dot structures on an undoped Si/SiGe heterostructure using an overlapping aluminum gate stackZajac et al. (2015). The two dimensional electron gas (2DEG) is formed in a 9 nm thick strained silicon layer either 20 or 30 nm below the surface. To avoid accumulation of 2DEG under the resonator, we remove the heterostructure everywhere except for two 50 x 100 mesa regions on the sample where the dot structures are located. The circuit consists of four key components: the overlapping aluminum gate electrodes, the dot lead wiring, the superconducting microwave resonator, and the resonator DC voltage tap. An optical image of a finished device is shown in Fig. 1 (a). To understand the control environment of the device, Fig. 1 (b) provides a simplified circuit diagram illustrating the key components the on-chip microwave engineering. Additional wires and parasitic cross capacitances are not drawn for simplicity. We confine the 2DEG into quantum dots using three layers of overlapping aluminum gates patterned with e-beam lithography (Fig. 1 (c)) and deposited by e-beam evaporation. High yield electrical isolation between gate layers is achieved by cleaning and oxidizing the aluminum after lift-off of each layer with a 250 W downstream oxygen plasma asher for 10 minutesDodson et al. .

Measurements of these samples are performed by wire bonding each device in a hybrid PCB-metal box enclosure designed to raise unwanted chip-mode frequencies to >20 GHz by creating a milled pocket below most of the 6.15 x 6.15 die Wenner et al. (2011). The packaged sample is cooled in a dilution refrigerator with base a temperature of and typical electron temperatures between 80-100 mK determined by fitting to a thermally broadened conductance peakBeenakker (1991). Charge detection is achieved by measuring the cavity-charge interaction during electron tunneling eventsFrey et al. (2012); Mi et al. (2017). These interactions are formed by connecting a gate (in our case P2 in Fig. 1 (c)) to an aluminum or niobium microwave resonator. Zero point fluctuations in the electric potential of the LC oscillator couple to the dipolar (quadrupolar) detuning degree of freedom () for the charge in the double (triple) dot system, allowing for detection of the quantum capacitance . By probing the cavity with a microwave tone at the bare cavity frequency () and recording the transmitted amplitude and phase as a function of plunger gate voltage, damping and phase shifts of the probe are observed during electron tunneling events when the rates are comparable to the cavity frequency (of order several GHz). In the overlapping gate architecture, this condition is easily achieved through tuning of the dot barrier gate voltages B1-B4. Using the plunger gates P1-P3, we can empty out the electrons in a double (or triple) dot and reach the (0,0) (or (0,0,0)) charge state configuration, as demonstrated in Fig. 1 (d).

In order to maintain a high cavity quality factor we engineer the microwave environment to minimize photon leakage out the 25 bias leads of the two triple dot gate structures. This engineering amounts to maximizing the reflection coefficient of the microwave energy out any lead other than the readout port by making the other leads look like high or low impedance to ground. A unique requirement for cQED experiments with dots is DC voltage biasing of the center pin of the coplanar waveguide (CPW) resonator in order to accumulate a quantum dot under P2. Test devices with DC taps at the center of the waveguide had quality factors less than , which was much lower than the explicit coupling defined by and . We eliminate leakage out this lead by turning the tap into a -length CPW. The end of the CPW is shunted with a load impedance in the form of a large parallel plate capacitor using an dielectric. The input impedance for a segment of transmission line terminated by a load is given byPozar (2011)

| (1) |

where is the propagation constant of the transmission line, and is its physical length. By making the shunt capacitance large ( pF), we achieve . In combination with tapping at the voltage node, this effective impedance leads to minimal leakage out the DC bias tap at the resonance frequency. Using this DC bias, devices without the overlapping aluminum gates achieved loaded quality factors as high as , well beyond the limit imposed by parasitic loading from the quantum dot circuit. We note that the quadratic dependence of on provides a way to further increase the quarter-wave tap input impedance through use of large CPWsSamkharadze et al. (2018).

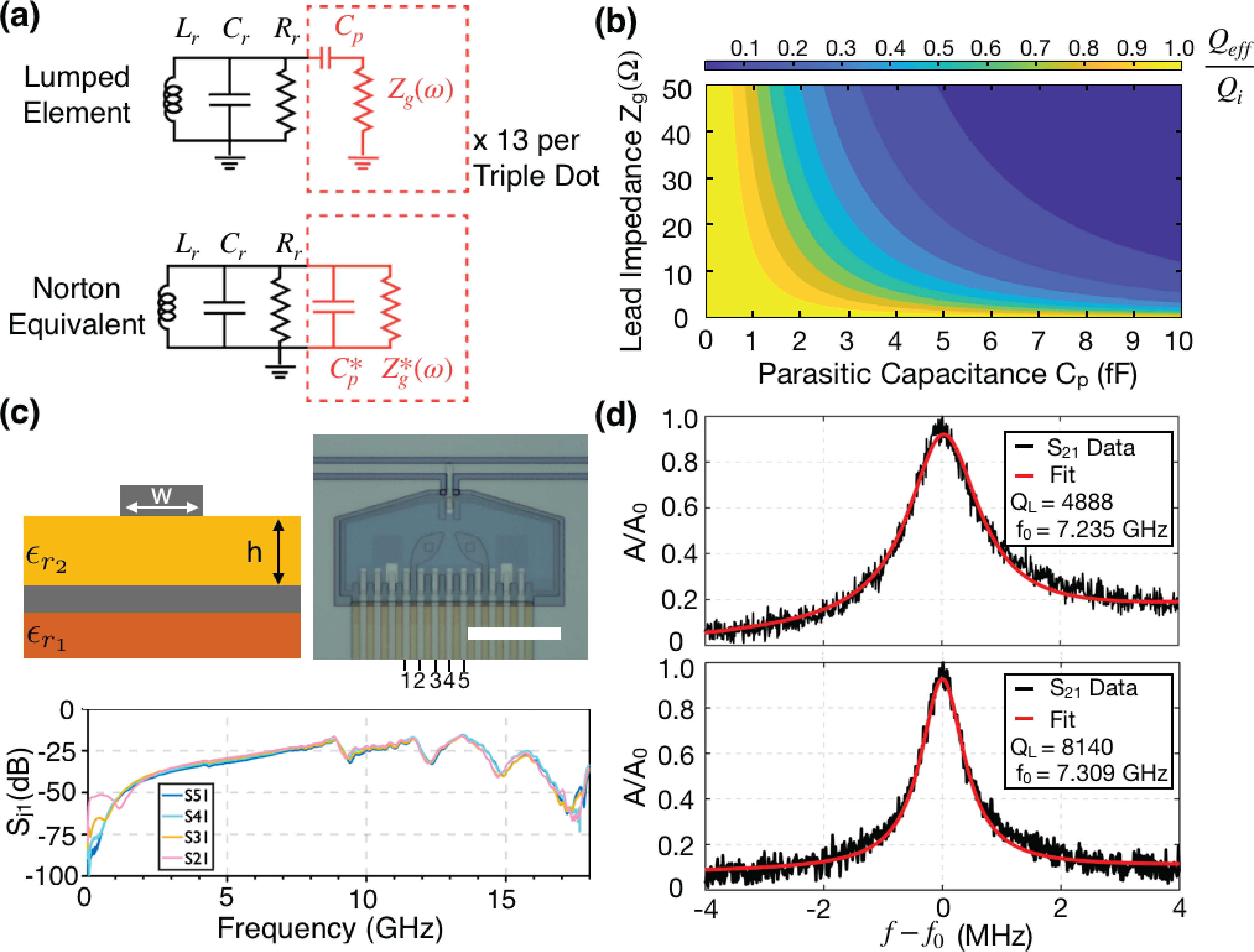

The use of the overlapping gate stack poses a unique challenge for RF readout schemes, because of the large parasitic capacitances (order 1 fF) between the gate electrodes in the region where the dots are formed. These parasitic capacitances are the same order of magnitude as the capacitance used to purposefully couple photons into the readout port ( fF for a quality factor of at 7.25 GHz) and therefore result in substantial microwave leakage out the leads. To analyze this leakage we first use a lumped element circuit model for loading of an LCR oscillator to a transmission line environment with characteristic impedance and parasitic capacitance Pozar (2011); Göppl et al. (2008). We then extend this model to real circuits with finite length leads where the general transmission line impedance transformer behavior captured in Eq. (1) must be taken into account. After including finite length effects we show that the intuition from the lumped element model is qualitatively correct as long as dot gate lead lengths sufficiently avoid half integer multiples of the resonance wavelength (e.g. for ).

For the lumped element analysis, we write the resonator intrinsic quality factor as . Here is the effective damping resistance arising from the lossy dielectrics coupled to the electric field of the resonator. Schematically, each dot lead looks like the series combination of a capacitance and, in the limit of an infinite transmission line, an effective real impedance to ground (Fig. 2 (a)). In the Norton equivalent circuit the gate impedance transforms to an additional parallel resistance

| (2) |

By computing the new total load resistance , we find the effective quality factor . In terms of the impedance of the parasitic capacitor , gate impedance , and effective internal resistance we find:

| (3) |

revealing there are in principle two ways for reducing the effect of unwanted loading: minimize the parasitic capacitance (maximizing ) or alter the gate impedance to minimize the effect of the term in the denominator of Eq. (3). Notably, it is easier to reach the limit of than , as for typical superconducting resonators. Figure 2 (b) shows a contour plot of Eq. (3) in the low regime. For our experiments, the characteristic cavity impedance is , but the core result holds for higher impedance cavities as well and is captured by the definition of .

Since reducing the parasitic capacitance in the overlapping gate stack is intrinsically difficult, we opt to control the gate impedance . Previous efforts to improve cavity quality factors involve the use of RF choke inductors or LC low pass filters, which have either high or low impedance at the cavity frequency, suppressing leakageFrey et al. (2012); Mi et al. (2017). In both cases, the leads acquire a frequency dependent filter function which substantially limits the control bandwidth. To eliminate this potentially undesired feature, we choose to reduce the characteristic impedance of the transmission line on-chip using a microstrip geometry. The design and implementation of microstrip wiring is illustrated in Fig. 2 (c). The wires are fabricated in a multilayer fabrication process that has three essential steps: deposition of the base layer ground plane, growth of an insulating dielectric layer, and deposition of the microstrip counter electrode.

To obtain the desired low impedance, we fabricate microstrips with a width and an thickness yielding the limit where the parameter . The impedance of the microstrip in this limit can be calculated using conformal mapping and is given byK.C. Gupta (1996); Pozar (2011):

| (4) |

with an effective permittivity:

| (5) |

For our parameters, we find which compares favorably to LC low pass filters in the literatureMi et al. (2017), that have an input impedance of , while retaining the flexibility of a flat frequency response. The low impedance leads come at the cost of an insertion loss of approximately 3.5 dB due to mismatch between the coaxial cabling and the microstrip. This effect could be mitigated by an impedance matching element such as a Klopfenstein taperK.C. Gupta (1996).

The multilayer stack also provides a means for improved and reliable microwave performance in increasingly complex processors through additional on-chip crossovers. These structures serve as low inductance connections between ground planes on-chip, thereby suppressing spurious slot line modes more efficiently than with traditional aluminum wire bond stitching Chen et al. (2014). Furthermore, aluminum wire bond stitching suffers from the low critical field of aluminum ( mT), which can damp the cavity upon application of an external magnetic fieldPetersson et al. (2012). Since both the crossover and base ground plane metals can be made of field tolerant superconductors such as niobium, they are useful for preserving circuit performance in cavity-spin coupling experiments. Lastly, in Fig. 2 (c) we demonstrate that this microstrip wiring scheme maintains less than -20 dB crosstalk between adjacent leads over a broad frequency range with a 7 m wire pitch for approximately 1 mm, which could be important for minimizing off-resonant driving observed in recent resonant two-qubit gate experimentsZajac et al. (2018); Sigillito et al. (2019).

Using these design principles, we fabricated and measured over twenty cavity coupled quantum dot structures and found a total spread in resonance quality factors between 2600-8140 (example spectra shown in Fig. 2 (d)). We attribute the spread in quality factor to variation in parasitic capacitance and finite length effects for the low impedance microstrips (discussed below). We note that in addition to the spread in quality factors for identical resonator designs (with lithographic variation of order 0.2 ), the fundamental resonance frequencies show a large spread of approximately MHz. Using the measured frequency, length of the waveguide, and conformal mappingK.C. Gupta (1996); Göppl et al. (2008) to estimate the capacitance of the CPW structure, we back out a mean substrate permittivity to be . Using linear interpolationSchaffler (2001) we estimate the permittivity of the SiGe alloy to be where . The origin of the apparent deviation is unknown at this time. Variation in the observed resonance frequencies could be explained by variation in the relative dielectric constant of the SiGe alloy by , possibly caused by fabrication processing or growth variation across the wafer.

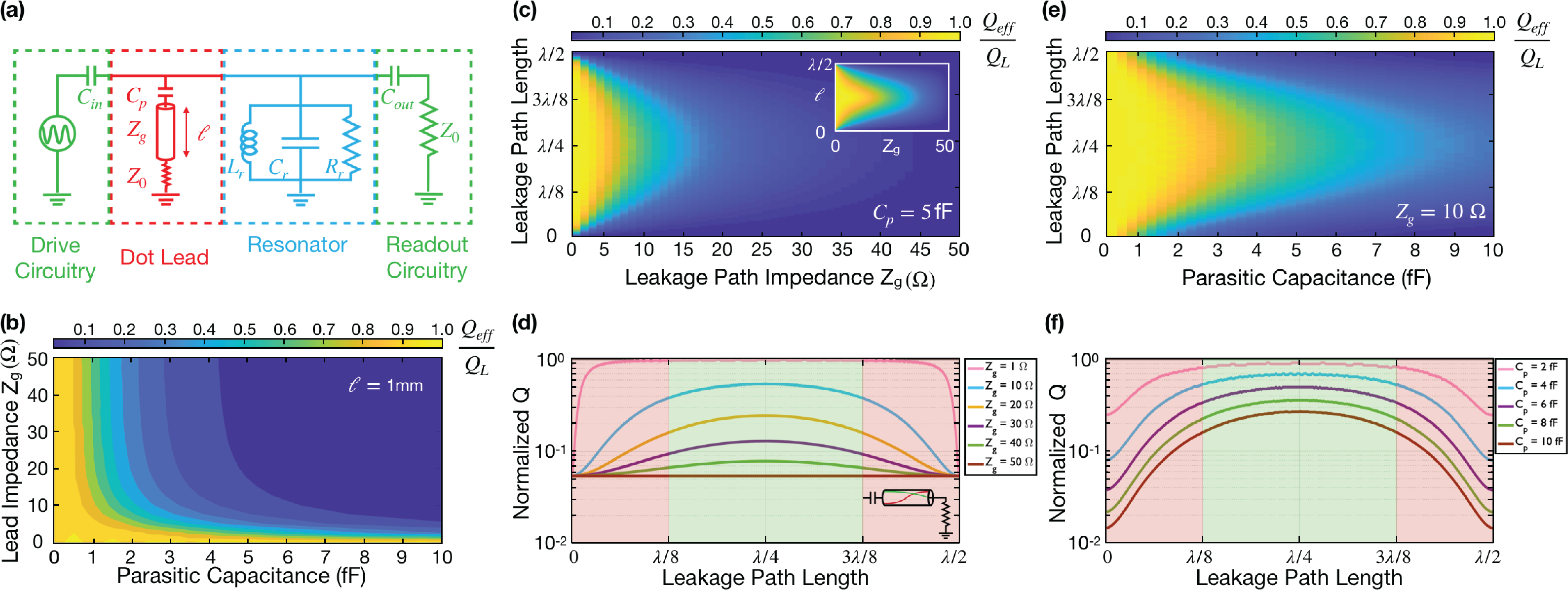

Although Eq. (3) is correctGöppl et al. (2008); Pozar (2011) for coupling to an infinitely long transmission line with impedance , in practice the low impedance leads on-chip are only a few millimeters long and are wire bonded to a environment. To elucidate the impact of the finite length of on-chip low impedance leads, we use "Simulation Program with Integrated Circuit Emphasis" (SPICE) to calculate the resonator line width under various conditions. Figure 3 (a) shows the circuit schematic used to understand the consequences of using finite transmission lines of length . Similar to the lumped element case, lowering and results in suppression of leakage. For a microstrip, the contour plot of the leakage path impedance in Fig. 3 (b) is qualitatively similar to that in Fig. 2 (b), but the roll-off is stronger as a function of .

In Fig. 3 (c,d) we compute as a function of and leakage path (gate) length. When the gate length is a quarter wavelength of the resonance frequency, no voltage drop occurs across the environment at the end of the lead, effectively eliminating loss out the lead. Conversely, when the lead is exactly in length, the voltage drop across the environment is maximal, resulting in loss to the environment equivalent to using no leakage suppression scheme at all. As shown in Fig. 3(c,d), if is low, the range of gate lead lengths that suppress leakage becomes very wide, with only lengths very close to displaying any significant degradation in . Figure 3 (e,f) shows that analogous results hold for as a function of . The inset to Fig. 3 (c) shows the reflection coefficient of a 50 terminated transmission line calculated using Eq. (1). The result is very similar to the SPICE calculation in the main panel, and thus the simple analytic form provides good intuition for the finite length effects in maintaining a high Q.

In conclusion, we demonstrated a high-density, low-crosstalk, low impedance wiring scheme for quantum dots in a cQED framework. Using a simple circuit model we designed a filterless low impedance wiring strategy for minimal microwave leakage achieving quality factors as high as 8140. We showed how this approach remains robust even in the presence of finite length effects of the low impedance leads. For devices with functional quantum dots, measurement of the charge configuration down to zero electrons in both double and triple dots is achieved, paving the way towards study of spin-photon coupling of exchange-based qubits in Si/SiGe Russ, Petta, and Burkard (2018).

The data that support the findings of this study are available from the corresponding author upon reasonable request.

We acknowledge discussions on multilayer superconducting circuit fabrication with A. Opremcak, E. Leonard, M. Beck, F. Schlenker, and M. Vinje. We acknowledge technical advice in development of processing recipes by K. Kuptcho, Q. Leonard, and E. Gonzales. Research was sponsored in part by the Army Research Office (ARO) under Grant Numbers W911NF-17-1-0274 and by the Vannevar Bush Faculty Fellowship program under ONR grant number N00014-15-1-0029. We acknowledge the use of facilities supported by NSF through the UW-Madison MRSEC (DMR-1720415) and the MRI program (DMR–1625348). The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the Army Research Office (ARO), or the U.S. Government. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein.

References

- Hanson et al. (2007) R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, “Spins in few-electron quantum dots,” Rev. Mod. Phys. 79, 1217–1265 (2007).

- Zwanenburg et al. (2013) F. A. Zwanenburg, A. S. Dzurak, A. Morello, M. Y. Simmons, L. C. L. Hollenberg, G. Klimeck, S. Rogge, S. N. Coppersmith, and M. A. Eriksson, “Silicon quantum electronics,” Rev. Mod. Phys. 85, 961–1019 (2013).

- Yoneda et al. (2018) J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, “A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%,” Nature Nanotechnology 13, 102–106 (2018).

- Veldhorst et al. (2015) M. Veldhorst, C. H. Yang, J. C. C. Hwang, W. Huang, J. P. Dehollain, J. T. Muhonen, S. Simmons, A. Laucht, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, “A two-qubit logic gate in silicon,” Nature 526, 410–414 (2015).

- Kawakami et al. (2016) E. Kawakami, T. Jullien, P. Scarlino, D. R. Ward, D. E. Savage, M. G. Lagally, V. V. Dobrovitski, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, “Gate fidelity and coherence of an electron spin in an Si/SiGe quantum dot with micromagnet,” PNAS 113, 11738 (2016).

- Zajac et al. (2018) D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, “Resonantly driven cnot gate for electron spins,” Science 359, 439–442 (2018).

- Sigillito et al. (2019) A. Sigillito, J. Loy, D. Zajac, M. Gullans, L. Edge, and J. Petta, “Site-selective quantum control in an isotopically enriched quadruple quantum dot,” Phys. Rev. Applied 11, 061006 (2019).

- Mi et al. (2018) X. Mi, M. Benito, S. Putz, D. M. Zajac, J. M. Taylor, G. Burkard, and J. R. Petta, “A coherent spin–photon interface in silicon,” Nature 555, 599 EP – (2018).

- Watson et al. (2018) T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, “A programmable two-qubit quantum processor in silicon,” Nature 555, 633 (2018).

- Fowler et al. (2012) A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, “Surface codes: Towards practical large-scale quantum computation,” Phys. Rev. A 86, 032324 (2012).

- Stockklauser et al. (2017) A. Stockklauser, P. Scarlino, J. V. Koski, S. Gasparinetti, C. K. Andersen, C. Reichl, W. Wegscheider, T. Ihn, K. Ensslin, and A. Wallraff, “Strong coupling cavity qed with gate-defined double quantum dots enabled by a high impedance resonator,” Phys. Rev. X 7, 011030 (2017).

- Samkharadze et al. (2018) N. Samkharadze, G. Zheng, N. Kalhor, D. Brousse, A. Sammak, U. C. Mendes, A. Blais, G. Scappucci, and L. M. K. Vandersypen, “Strong spin-photon coupling in silicon,” Science 359, 1123 (2018).

- Zajac et al. (2015) D. M. Zajac, T. M. Hazard, X. Mi, K. Wang, and J. R. Petta, “A reconfigurable gate architecture for si/sige quantum dots,” Applied Physics Letters 106, 223507 (2015).

- (14) J. P. Dodson, N. Holman, B. Thorgrimsson, S. F. Neyens, E. R. MacQuarrie, T. McJunkin, R. H. Foote, L. F. Edge, S. N. Coppersmith, and M. A. Eriksson, “Fabrication process and failure analysis for robust quantum dots in silicon,” arXiv:2004.05683 .

- Wenner et al. (2011) J. Wenner, M. Neely, R. C. Bialczak, M. Lenander, E. Lucero, A. D. O’Connell, D. Sank, H. Wang, M. Weides, A. Cleland, and J. M. Martinis, “Wirebond crosstalk and cavity modes in large chip mounts for superconducting qubits,” Supercond. Sci. and Technol. 24, 650001–7 (2011).

- Beenakker (1991) C. W. J. Beenakker, “Theory of coulomb-blockade oscillations in the conductance of a quantum dot,” Phys. Rev. B 44, 1646–1656 (1991).

- Frey et al. (2012) T. Frey, P. J. Leek, M. Beck, A. Blais, T. Ihn, K. Ensslin, and A. Wallraff, “Dipole coupling of a double quantum dot to a microwave resonator,” Phys. Rev. Lett. 108, 046807 (2012).

- Mi et al. (2017) X. Mi, J. V. Cady, D. M. Zajac, J. Stehlik, L. F. Edge, and J. R. Petta, “Circuit quantum electrodynamics architecture for gate-defined quantum dots in silicon,” Applied Physics Letters 110, 043502 (2017), https://doi.org/10.1063/1.4974536 .

- Pozar (2011) D. Pozar, Microwave Engineering, 4th ed. (Wiley, 2011).

- Göppl et al. (2008) M. Göppl, A. Fragner, M. Baur, R. Bianchetti, S. Filipp, J. M. Fink, P. J. Leek, G. Puebla, L. Steffen, and A. Wallraff, “Coplanar waveguide resonators for circuit quantum electrodynamics,” Journal of Applied Physics 104, 113904 (2008).

- K.C. Gupta (1996) I. B. P. B. K.C. Gupta, R. Garg, Microstrip Lines and Slotlines, 2nd ed. (Artech House, 1996).

- Chen et al. (2014) Z. Chen, A. Megrant, J. Kelly, R. Barends, J. Bochmann, Y. Chen, B. Chiaro, A. Dunsworth, E. Jeffrey, J. Y. Mutus, P. J. J. O’Malley, C. Neill, P. Roushan, D. Sank, A. Vainsencher, J. Wenner, T. C. White, A. N. Cleland, and J. M. Martinis, “Fabrication and characterization of aluminum airbridges for superconducting microwave circuits,” Applied Physics Letters 104, 052602 (2014), https://doi.org/10.1063/1.4863745 .

- Petersson et al. (2012) K. D. Petersson, L. W. McFaul, M. D. Schroer, M. Jung, J. M. Taylor, A. A. Houck, and J. R. Petta, “Circuit quantum electrodynamics with a spin qubit,” Nature 490, 380 EP – (2012).

- Schaffler (2001) F. Schaffler, Properties of Advanced SemiconductorMaterials GaN, AlN, InN, BN, SiC, SiGe (Wiley, 2001).

- Russ, Petta, and Burkard (2018) M. Russ, J. R. Petta, and G. Burkard, “Quadrupolar exchange-only spin qubit,” Phys. Rev. Lett. 121, 177701 (2018).

- Zajac et al. (2016) D. M. Zajac, T. M. Hazard, X. Mi, E. Nielsen, and J. R. Petta, “Scalable gate architecture for a one-dimensional array of semiconductor spin qubits,” Phys. Rev. Applied 6, 054013 (2016).