QECC-Synth: A Layout Synthesizer for Quantum Error Correction Codes on Sparse Hardware Architectures

Abstract

Quantum Error Correction (QEC) codes are essential for achieving fault-tolerant quantum computing (FTQC). However, their implementation faces significant challenges due to disparity between required dense qubit connectivity and sparse hardware architectures. Current approaches often either underutilize QEC circuit features or focus on manual designs tailored to specific codes and architectures, limiting their capability and generality. In response, we introduce QECC-Synth, an automated compiler for QEC code implementation that addresses these challenges. We leverage the ancilla bridge technique tailored to the requirements of QEC circuits and introduces a systematic classification of its design space flexibilities. We then formalize this problem using the MaxSAT framework to optimize these flexibilities. Evaluation shows that our method significantly outperforms existing methods while demonstrating broader applicability across diverse QEC codes and hardware architectures.

I Introduction

Current quantum devices [1, 2, 3] suffer from errors, limiting their effectiveness in various applications [4, 5]. Quantum error correction (QEC) addresses this issue by encoding redundant physical qubits into logical qubits [6]. These logical qubits exhibit significantly lower error rates, ensuring the fidelity of quantum computations [7, 8]. Recent advancements in small-scale QEC implementations [9, 10, 11] demonstrate progress toward large-scale FTQC.

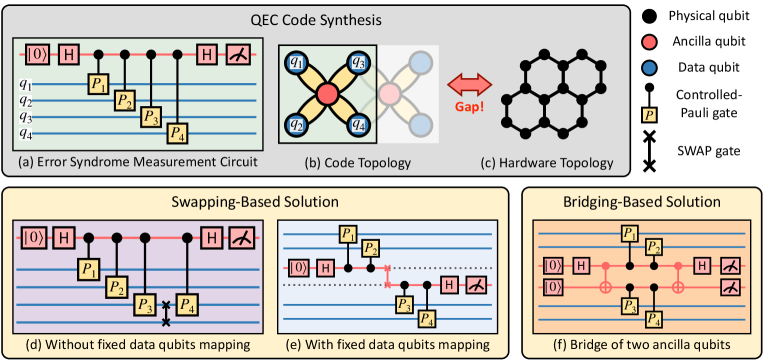

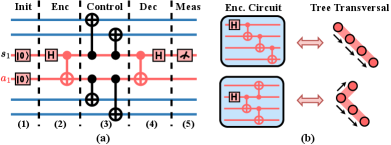

The core of QEC lies in the error syndrome measurement (ESM) circuits constructed from the QEC codes [12, 13, 14, 15, 16, 17, 18]. A typical ESM circuit (Fig. 1(a)) includes an syndrome qubit (red) and multiple data qubits (blue). Controlled gates (yellow) entangle the syndrome qubit with the data qubits, allowing errors on the data qubits to affect the syndrome qubit’s state and flip its measurement outcome, indicating error occurrence. Hundreds or even more such ESM circuits are executed in a QEC cycle to gather error information across the logical qubit spanning numerous data qubits. For example, a typical distance- surface code has data qubits per logical qubit and needs such ESM circuits in a QEC cycle. This QEC cycle repeats during the runtime to safeguard the quantum system against errors.

However, implementing these circuits on current hardware presents a great challenge due to the mismatch between code topology and hardware architecture [19, 20, 21, 22, 23]. For instance, surface codes [18], a well-studied QEC code, requires a qubit connectivity of degree (Fig. 1(b)) to enable interactions between the syndrome qubit (red) and four data qubits (blue) in their ESM circuits (Fig. 1(a)). In contrast, current hardware (Fig. 1(c)) typically has sparser architectures with connectivity degrees of or [24, 25, 5, 10, 26, 27] due to technical constraints [28, 29, 30]. Given the variety of QEC codes and hardware architecture, this gap is expected to persist in the foreseeable future.

A natural approach to tackle this issue involves swapping-based methods used in qubit mapping and routing (QMR) problems [31, 32, 33]. They insert SWAP gates into circuits to route distant qubits adjacent for interaction. For example, in Fig. 1(a), to execute a controlled- gate between the syndrome qubit and distant data qubit , a SWAP gate is used to relocate to ’s position. However, altering qubit locations with these methods is unsuitable for ESM circuits because the QEC process requires consistent data qubit positions for repeated execution [34]. A potential solution is to enforce fixed data qubit locations as in Fig. 1(e). However, achieving this reliably with current methods may require exponentially increasing attempts as QEC circuit complexity grows.

Beyond swapping-based methods, theoretical research [35, 20, 36, 37] introduces ancilla qubits in circuit mapping to form an “ancilla bridge” that connects data qubits (marked red in Fig. 1(f)), termed bridging methods. Compared to swapping-based methods, they fix the qubit locations and use fewer CNOT gates (2 CNOTs compared to 3 CNOTs in a SWAP gate). However, current research primarily focuses on theoretical aspects and has made limited attempts only on manual designs targeting specific codes and architectures, mostly for small-scale problems. For instance, [35] manually implement the 7-qubit Steane code on a square lattice, while heuristic methods [19, 20] adapt the surface code [18] to regular lattices like heavy-hexagon [20] up to distance 5. These specific manual designs lack adaptability to newer QEC codes like qLDPC codes [38, 39] and future hardware architectures. Moreover, these methods assume ideal hardware structures and struggle with variations caused by defective qubits [40, 41, 42], an issue gaining recent attention [43, 44].

We identified a crucial oversight in previous bridging methods: neglecting the broad design space enabled by ancilla qubits. Theoretically, bridging methods allow for diverse ancilla bridge shapes and sizes, various ancilla sharing designs, and flexible gate scheduling (Section III). However, current methods rely on heuristic and manual designs, missing out on these flexibilities. This severely restricts the range of potential solutions, essentially limiting their generality.

Based on this insight, we introduce QECC-Synth, the first automated compiler for mapping ESM circuits using bridging methods applicable to diverse QEC codes and hardware architectures. To achieve this, we for the first time systematically categorize the flexibility of bridging methods into two key aspects: (1) ancilla bridge and (2) circuit optimization (Section III). We then identify two critical metrics for selecting optimal solutions related to these flexibilities: (1) extra CNOT gates in ancilla bridge construction and (2) total circuit depth. Minimizing these metrics is crucial for reducing physical errors and decoherence, thereby improving circuit fidelity. Therefore, we formalize the ESM circuit mapping into two optimization problems: code topology mapping and gate scheduling (Sections V-A and V-B), targeting the above two metrics. By translating code structures, hardware architectures, and mapping/scheduling conditions into Boolean constraints, we frame these optimization problems into MaxSAT framework, solvable by SAT solvers [45]. Importantly, our unified approach accommodates diverse codes and hardware setups, including systems with defective qubits. Furthermore, to handle large-scale problems, we introduce a heuristic algorithm that partitions them into manageable sub-problems addressed by our MaxSAT framework (Section V-C).

We evaluate our method against three baselines: (1) Sabre (heuristic, swapping-based) [31], (2) SATmap (solver-based, swapping-based) [33], and (3) Surf-Stitch (heuristic, bridging-based, targeting surface codes) [19]. Our method achieves an average reduction of 74.9% and 26.5% in extra CNOT gate counts, and 34.7% and 55.5% in circuit depth compared to Sabre and SATmap, respectively. Our method also outperforms the surface-code-specific approach Surf-Stitch with 10% fewer extra CNOT gates and 38.5% shallower circuits. Additionally, these baselines frequently fail to provide solutions for special QEC codes and hardware setups and exceed memory limits for large-scale problems (Section VI). In contrast, our approach consistently identifies viable solutions.

Overall, we make the following contributions:

-

•

We introduce QECC-Synth, a bridging-based compiler for efficiently mapping ESM circuits, supporting diverse QEC codes and hardware architectures.

-

•

We pioneer the exploration of the expansive design space of bridging methods and formalize ESM circuit mapping as a two-stage MaxSAT problem.

-

•

We propose a heuristic approach based on our MaxSAT framework to effectively handle scalability challenges with large-scale codes.

-

•

Our evaluation shows that QECC-Synth outperforms existing swapping-based and bridging-based methods across various QEC codes and hardware setups, while also demonstrating good scalability.

II Background

In this section, we provide essential background information on ESM circuits implementation.

II-A ESM Circuits for Stabilizer Codes

We focus on stabilizer codes [6, 46] that encompass most extensively studied QEC codes [47, 48, 18].

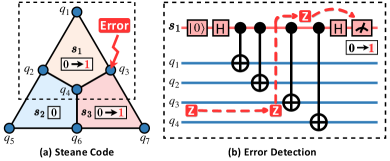

Stabilizer codes. Stabilizer codes are characterized by a set of stabilizers, which are Pauli strings of the form , where denotes a Pauli operator acting on qubit . For instance, Fig. 2(a) gives a stabilizer code with stabilizers . Each stabilizer collects error information on its involved qubits, and combining this information from all stabilizers helps to deduce the type and location of errors, facilitating appropriate corrections. In practice, this process of error information collection involves implementing a dedicated error syndrome extraction (ESM) circuit for each stabilizer.

ESM circuits. The ESM circuit of a stabilizer comprises a syndrome qubit (red) and several data qubits (blue), connected by controlled gates specified by the stabilizer. The syndrome qubit is initially set to the state and is measured at the end. If there are no errors on the data qubits, the measurement outcome is still . Conversely, certain errors on the data qubits will propagate through the controlled gate to the syndrome qubit, flipping its measurement outcome from to , indicating error occurrence. For instance, as shown by the red dashed line in Fig. 2(b), a -error on qubit propagates through the CNOT gate and flipsthe measurement outcome of . Notably, stabilizers often share data qubits, which introduces complexity to the mapping and scheduling of their ESM circuits (more details in Section III).

Error detection and correction. During a QEC round, each ESM circuit is executed once. Their measurement results consist error syndromes that guide error correction. For instance, in Fig. 2(a), the error syndrome suggests a -error on qubit , which can be corrected by applying a gate to since . Crucially, all ESM circuits can theoretically operate in parallel within a QEC round due to the commutativity of stabilizers, allowing for a larger optimization space for scheduling (more details in Section III).

II-B Bridging method

ESM circuits necessitate interactions between the syndrome qubit and all data qubits, which is challenging with hardware of limited connectivity. The bridging method [35] offers a promising solution by extending the syndrome qubit with additional ancilla qubits called bridge qubits, forming an “ancilla bridge” that connects distant data qubits. This approach resolves connectivity issues while maintaining error syndrome extraction as in the original ESM circuit.

Mitigating connectivity issue. In bridging method, the ancilla bridge is prepared in a special entangled state [49] by inserting additional CNOT gates (highlighted in red). This state ensures that the controlled gates acting on the syndrome qubit can be transferred to the bridge qubit while maintaining circuit equivalence. As a result, the connectivity requirements, originally concentrated on the single syndrome qubit, are now distributed across multiple bridge qubits, thereby reducing the overall connectivity demand. For instance, the circuit with a length-2 ancilla bridge in Fig. 3(b) only requires each qubit to connect to at most 3 others, compared to 4 in Fig. 2(b), allowing for a direct mapping to current sparse quantum architecture [24, 25, 5, 26].

Error syndrome extraction. Remarkably, the ancilla bridge construction ensures that errors on the data qubits trigger a flip in the measurement result of the syndrome qubit, just as in the original ESM circuit (Fig. 2(b)). This occurs because errors can still propagate to the syndrome qubit through the special entangled state of the ancilla bridge (GHZ state). For instance, in Fig. 3(b), a -error on still flips the measurement result of the syndrome qubit (as shown by the red dashed line). Consequently, the transformed ESM circuit with bridge qubits preserves the same error detection and correction capabilities as the original circuit.

Impact of extra CNOT gates. Bridging methods introduce additional CNOT gates (highlighted in red) compared to the original ESM circuit (Fig. 2(b)). Similar to the extra CNOT gates in SWAP-based methods, these CNOTs can introduce errors to data qubits, potentially increasing the logical error rate. For example, in Fig. 3(b), if a -error occurs due to an introduced CNOT gate (within the block), it can induce a correlated two-qubit error on data qubits and affect the accuracy of the syndrome measurement. Therefore, minimizing the number of CNOT gates is crucial to mitigate these detrimental effects.

III Motivating Examples

In this section, we provide examples to illustrate the vast design space of bridging-based ESM circuit mapping and scheduling. We highlight two main flexibilities: (1) varying ancilla bridges to optimize qubit mapping with fewer CNOT gates, and (2) leveraging circuit commutativity and equivalence to optimize gate scheduling for reduced circuit depth.

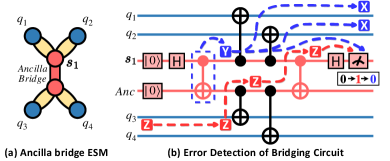

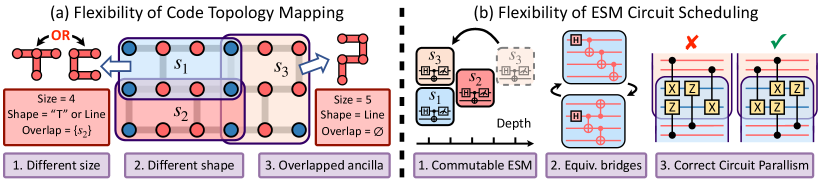

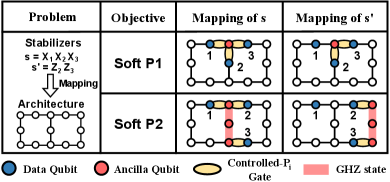

III-A Flexibility of Code Topology Mapping

Ancilla bridges offer significant flexibility, particularly in terms of (1) various shapes and sizes and (2) shared ancilla qubits. This flexibility helps to find an effective mapping of the stabilizer code’s topology onto the architecture, including the data qubit mapping and the ancilla bridge allocation. Moreover, varying constructions can introduce different numbers of CNOT gates (Section II), impacting the fidelity of the synthesized ESM circuits. Since the total size of the ancilla bridge linearly correlates with the number of extra CNOT gates, we prioritize minimizing it as our optimization goal in code topology mapping (Section V).

(1) Various shapes and sizes. The flexibility of ancilla bridges extends to their shapes and sizes, which stems from their operational mechanism. As long as the ancilla bridge is initialized in an entangled state, errors on data qubits can propagate to the syndrome qubit regardless of which bridge qubit they are connected to. Thus, the circuit can extract the error syndrome, irrespective of the ancilla bridge’s shape or size. Consequently, the shape and size of the ancilla bridge can vary depending on the allocation of data qubits. For example, as shown in Fig. 4(a), both the 4-qubit and 5-qubit ancilla bridges for and can effectively fulfill their function, demonstrating this flexibility. For more details, we recommend referring to Lao et al. [35].

(2) Ancilla qubit sharing. Ancilla bridges for different stabilizers can share the same ancilla qubits, reducing the number of ancilla qubits required to be connected to a data qubit. For example, in Fig. 4(a), stabilizers and share two ancilla qubits in the middle row. Although this design saves qubits, ESM circuits sharing ancilla qubits cannot be executed simultaneously due to resource conflicts. This presents a challenge for gate scheduling to optimize parallel executions.

III-B Flexibility of ESM Circuit Scheduling

The distinctive structures of ESM circuits allow for more flexible optimizations in scheduling compared to the gate-level scheduling for general quantum circuits. This flexibility arises mainly from three aspects: (1) commutativity of stabilizer measurements, (2) equivalent state preparations on ancilla bridges and (3) parallel ESM circuits. Leveraging this flexibility, our goal is to identify a correct scheduling while minimizing the circuit depth.

(1) Commutable stabilizer measurements. Implementing a QEC code involves executing ESM circuit blocks (Fig. 2(b)) for all stabilizers. Theoretically, these ESM circuit blocks for various stabilizers commute, allowing for arbitrary permutations in their order. As illustrated in Fig. 4(b1), sequentially executing stabilizer blocks , , and can be optimized by moving to the front and executing it in parallel with , leading to a substantial decrease in circuit depth.

(2) Equivalent state preparations on ancilla bridges. As explained in Section II, the ancilla bridge is initialized in an appropriate entangled state. This initialization can be accomplished through various circuits and some of which may offer smaller circuit depths [49]. For instance, in Fig. 4(b2), both circuits can prepare the 4-qubit initial state on the ancilla bridge of , but the second one has a smaller circuit depth.

(3) Parallel ESM circuits. Although two ESM circuits can be executed in parallel as long as their ancilla bridges do not overlap, the overlap on data qubits makes it impossible to arbitrarily order the controlled gates while still ensuring a correct error syndrome extraction. To illustrate, as depicted in Fig. 4(b3), the simultaneous measurement of two stabilizers and , which share two data qubits, poses a challenge for the scheduling of their controlled- and controlled- gates. While the second circuit provides correct measurement results, the first one can only yield random outcomes [18]. This necessity for correctness adds intricacy to scheduling and must be addressed accordingly.

IV Overview of QECC-Synth

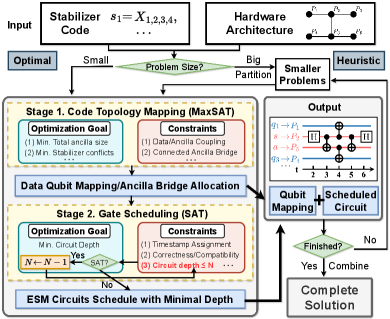

This section outlines the workflow of our QECC-Synth framework. It splits into two paths based on problem size, as shown in Fig. 5. For small-scale problems, QECC-Synth utilizes our dedicated two-stage SAT solver (Fig. 5, left frame) to generate optimal ESM circuit implementations. For large-scale problems, we employ the relaxation technique of problem partitioning to resolve the scalability issue (Fig. 5, right).

IV-A Constraint-based Approach: Two-stage SAT

The left frame in Fig. 5 represents the central component of the QECC-Synth framework. It takes the stabilizer code and hardware architecture as inputs and generates the ESM circuit implementation, specifying both qubit allocation and scheduled circuit. Building on the two flexibility categories identified in Section III, we break down this problem into two stages of constraint-based optimization: Stage 1. Code topology mapping and Stage 2. ESM circuit scheduling.

Stage 1. Code Topology Mapping. This stage aims to map data qubits and allocate ancilla bridges based on the stabilizer code and hardware architecture. The code is represented by its stabilizer set , where are Pauli strings acting on data qubits , while the hardware architecture is represented by its coupling graph, with vertices being physical qubits and the edges specifying their connectivity. The output consists of: (1) Data qubit mapping that map data qubits to physical qubits on hardware, (2) Ancilla bridge that allocate an ancilla bridge for each stabilizer, and (3) Coupling relation that specifies the ancilla qubit to which each data qubit connects in each stabilizer.

We address this problem using the MaxSAT framework. The validity of the output is ensured by various constraints (red frame), while optimality is pursued by maximizing an objective function composed of a weighted sum involving multiple optimization goals (blue frame). For instance, we minimize the overall size of ancilla bridges, which directly impacts the number of introduced CNOT gates (Section III), and maximize the number of compatible stabilizers to enable parallel execution. The corresponding objective function is:

Adjusting the weights alters the priority of optimization goals. The detailed MaxSAT encoding of constraints and objective function will be elaborated in Section V.

Stage 2. Gate Scheduling. This stage aims to find a gate scheduling with minimal circuit depth, based on the qubit allocation determined in Stage 1. The output is a mapping that assigns each gate a time step for execution. The search process is encoded into a SAT solver, with constraints (detailed in Section V) specified to ensure scheduling validity. To minimize circuit depth, we iteratively query the SAT solver with decreasing requirements on circuit depth until no solutions are found. This iterative approach helps obtain increasingly better solutions with smaller circuit depths, finally leading to a solution with minimal depth.

The outputs of the above two stages together constitute the complete output of our framework, specifying the mapping of data qubits and ancilla bridges, as well as the time schedule of each gate in the ESM circuit.

IV-B Heuristic Approach: Code Partitioning

The optimal approach described in Section IV-A faces challenges when applied to large-scale problems due to the escalating number of constraints. To address this scalability concern, we partition the stabilizer set of a code into smaller subsets and leverage our two-stage optimal solver described in Section IV-A to find their implementations. This yields optimized ESM circuits for each subset . Subsequently, we sequentially execute these ESM circuits for sub-problems to generate the complete solution for the entire stabilizer code. SWAP gates are inserted between adjacent ESM circuits to reposition the qubits from the previous circuit to meet the requirements of the next one (detailed in Section V). The evaluation (Section VI) shows that our approach enables scalability while yielding favorable results.

V Constraint-Based Code Synthesis

In this section, we delve into the technical aspects of SAT encoding for the two stages in QECC-Synth: code topology mapping and ESM circuit scheduling.

V-A Stage 1: Code Topology Mapping via MaxSAT

In this stage, we encode the mapping of data qubits and the allocation of ancilla bridges into a MaxSAT problem. We formulate the qubit location requirements as hard constraints and the objectives of minimizing the total ancilla bridge size and incompatible stabilizer count as soft constraints.

V-A1 Hard Constraints:

We list a few hard constraints that ensures the validity of qubit allocation.

Hard A. Basic Requirements. A legitimate qubit allocation should satisfy the following basic requirements.

(1) Each data qubit is mapped to a unique physical qubit:

where if data qubit is mapped to physical qubit , and otherwise.

(2) A physical qubit cannot serve as both a data qubit and an ancilla qubit simultaneously:

where if physical qubit is an ancilla qubit for stabilizer , and otherwise.

Hard B. Connectivity of ancilla bridge. The ancilla bridge for each stabilizer needs to form a connected graph. To ensure this, we employ breadth-first traversal (BFT) [50]. All physical qubits in the connected must be visited within a specified parameter , representing the maximum size of the ancilla bridge for stabilizer . We introduce auxiliary variables to track whether physical qubit has been visited after the -th round (). In the initial round, we ensure that the starting vertex is visited:

In subsequent rounds, an unvisited physical qubit in the ancilla bridge is visited if any of its adjacent qubits have been visited in the previous rounds:

To ensure that the traversal starts from any possible physical qubit, we enforce constraints for each :

The number of variables and the conjunctive normal form (cnf) clause used for each stabilizer are both .

Hard C. Coupling between data and ancilla qubits.

Each data qubit for stabilizer must be directly coupled to some ancilla qubit in its ancilla bridge :

(1) Exactly one ancilla qubit is coupled with data qubit :

(2) The coupling relation requires to be mapped to some qubit adjacent to :

V-A2 Soft Constraints:

We introduce several soft constraints to optimize the performance of ESM circuit implementation. Each soft clause is assigned a non-negative weight indicating its priority, and a MaxSAT solver is used to obtain a solution that maximizes the sum of the weights of all satisfied soft clauses.

Soft P1. Minimizing the total ancilla bridge size. Reducing the total ancilla bridge size compresses the ESM circuit and minimizes the introduced extra CNOT gates, enhancing circuit fidelity. This is achieved by maximizing the number of Boolean variables set to . Hence, we add the following soft constraints with weight :

Soft P2. Mitigating the stabilizer conflicts. Stabilizers without conflicts in ancilla qubits can be efficiently executed in parallel, termed as compatible stabilizers. Our aim is to maximize the count of compatible ancilla bridge pairs. Thus, we introduce the following soft constraints with weight :

Fig. 6 illustrates how different optimization objectives impact the mappings of the same code onto a heavy square architecture. In the first row, Soft P1 is the primary objective, with weight notably greater than . Consequently, the resulting mapping features an ancilla bridge with size , yet two stabilizers share the same ancilla qubit. Conversely, in the second row, Soft P1 is prioritized, resulting in a mapping without conflicts in data qubits, albeit with a larger ancilla bridge size. In practice (Section VI), we prioritize Soft P1 over Soft P2, given its more significant impact on the overall error correction performance.

V-B Stage2: ESM Circuit Scheduling via SAT

This stage encodes the gate scheduling of ESM circuits into a SAT problem. We introduce additional Boolean variables to characterize all operations within the circuits (Section V-B1). These variables help to formulate constraints based on dependencies between operations, ensuring the validity of their scheduling (Section V-B2). Finally, we iteratively query the SAT solver to achieve a scheduling with minimal circuit depth.

V-B1 Operations within ESM Circuits:

A ESM circuit with ancilla bridge typically comprises five phases: (1) Initialization, (2) Encoding, (3) Control, (4) Decoding, and (5) Measurement, as shown in Fig. 7(a). Operations in Phases (1)(3)(5) are determined by the output of Stage 1, which includes qubit allocation and coupling relations between ancilla and data qubits. Specifically, qubit allocation specifies all ancilla qubits initialized in the state, with the syndrome qubit measured at the end, constituting Phases (1)(5). The coupling relation precisely determines all CNOT gates in Phase (3). To characterize Phases (2)(4), we introduce the following Boolean variables:

and : The variable is set to if there is a gate from to in the Encoding phase for stabilizer , and otherwise. Similar definitions apply to . Additionally, a Hadamard gate is applied to the syndrome qubit. These Boolean variables collectively characterize the operations in Phases (2)(4).

: This denotes the time assignment of operations . If the operation is executed at time , is set to ; otherwise, it is set to .

V-B2 Boolean Constraints for Gate Scheduling:

This section outlines the constraints that must be satisfied by a valid gate scheduling, using the variables defined above.

Hard A. Time Assignment Constraints.

A valid gate scheduling should satisfy the following basic requirements regarding time assignments. We define as the maximum allowable circuit depth for the search.

(1) All gates should be executed exactly once:

(2) Two operations and act on the same physical qubit cannot be executed simultaneously. In other words, at most one operation acting on can be executed at time :

where denotes all the operations acting on .

Hard B. Valid and circuits. The circuits in the Encoding and Decoding phases should effectively encode and decode the GHZ state for the ancilla bridge. We observe that the encoding circuit’s formulation is analogous to a tree traversal, where the syndrome qubit serves as the root with an H gate acting on it, and other ancilla qubits are visited via CNOT links (Fig. 7(b)). The decoding circuit can be viewed as the mirror image of the encoding circuit. With this understanding, we establish the following constraints:

(1) The transversal tree must have exactly one root:

where is set to if an H gate acts on physical qubit , and otherwise.

(2) Each node within the transversal tree is visited exactly once, ensuring that every ancilla qubit is subjected to exactly one gate targeting it:

(3) The control qubit must be prepared before its associated CNOT gate is executed. Specifically, if and , then must be executed after :

Hard C. Correct order of circuits. The anticommuting controlled- gates in the Control phase should satisfy a particular order to ensure the correctness of the circuit. Specifically, the order is correct if and only if the count of anti-commuting gate pairs satisfying is an even number. This requirement is encoded into the constraint:

where means the mod 2 addition and means and anti-commute.

Hard D. Commutativity of incompatible stabilizers. Two stabilizer circuits and sharing ancilla qubits cannot he executed simultaneously. This constrain can be realized by requiring after , after :

where represent all physical qubit that shared by two stabilizer’s ancilla block.

V-C Heuristic Approach

As previously discussed, the number of clauses increases exponentially with the number of stabilizers in a QEC code, creating a significant bottleneck in our framework. To address this challenge for large-scale QEC code synthesis, we propose a relaxation method that can still yield locally optimal solutions. Our approach involves partitioning the set of stabilizers and solving a SAT problem for each subset sequentially through our two-stage constraint-based approach. Finally, we insert routing layers between the these synthesized ESM circuits to integrate them into the original code.

Partitioning the stabilizer set. We can think of a stabilizer set as a union of subsets, . However, due to the commutativity of the stabilizers, there are millions of possible partition choices. Since each stabilizer can be viewed as a set of constraints for the data qubits to satisfy, we want the constraints for the same data qubits to be in the same partition, allowing them to be handled together. It means to minimize the connections or shared qubits between stabilizers from different subsets. As a result, we formulate this as a simple balanced graph partitioning problem in graph theory [51]. For example, in the Steane code shown in Fig. 2(a), we treat each stabilizer as a vertex. As stabilizer shares two data qubits, and , with stabilizer , two edges will be added to the graph. The balanced graph partitioning divides the vertices into components of almost equal size, minimizing the capacity of edges between different components.

Sorting the SAT problems. After partitioning the stabilizer set, we can apply our two-stage SAT solver to synthesize the ESM circuit for each stabilizer subset. However, different resulting data qubit mappings can make it challenging to integrate them into a complete circuit for the original code. The mapping for subset should follow the mappings from to as closely as possible, because stabilizers from different subsets may share the same data qubits, and we want these qubits to be mapped to the same positions in . Therefore, after solving the SAT problem for , we select the subset that shares the most data qubits with all data qubits involved in as the next SAT problem to solve. Moreover, we add soft constraints in Stage 1 to maximize the number of shared data qubits that remain in their previous positions:

Integrating the ESM circuits. After all ESM circuits for each subset are generated, we connect them to form the complete ESM circuit for the original QEC code. Although the circuits may require different data qubit mappings and ancilla bridge allocations on the architecture, we insert integration layers between them to move the data qubits to meet these varying requirements. Since all ancilla qubits function identically and only data qubits contain the logical information, we only need to route the data qubits instead of all used physical qubits, as general QMR methods do. In the integration layer, to connect ESM circuits, we find the shortest path for each data qubit that changes its position and insert SWAP gates to move it to the new position.

VI IMPLEMENTATION AND EVALUATION

VI-A Experimental Setup

Evaluation setting: Our framework, QECC-Synth, utilizes the state-of-the-art MaxSAT solver, NuWLS-c [52], and the widely-used SAT solver, PySAT [53], with a solving time limit of 7,200 seconds and a memory limit of 128 GB. For logical error analysis, we used Stim [54], a widely-used QEC simulator for ESM circuits, and PyMatching [55], a error syndrome decoder that implements the Minimum Weight Perfect Matching (MWPM) algorithm.

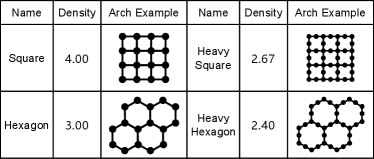

Hardware architectures: We cover a diverse range of practical device architectures in our evaluation. As shown in Fig. 8, the selected architectures are sourced from the latest quantum machines, including Google’s Sycamore [5], IBM’s Osprey, and IBM Q Tokyo [2]. To represent the connectivity of the architecture, we use the average degree of the nodes, denoted as .

| Code | Density | Architecture | # qubit | # Extra CNOT gate | Circuit depth | ||||

| QECC-Synth | SATmap | Sabre | QECC-Synth | SATmap | Sabre | ||||

| Surface Code | 2.82 | Square | 25 | 0 | 0 | 30 | 8 | 17 | 16 |

| Hexagon | 21 | 14 | 27* | 90 | 19 | 34* | 35 | ||

| H-Square | 29 | 24 | 42* | 90 | 20 | 49* | 21 | ||

| H-Hexagon | 46 | 56 | 66* | 96 | 16 | 47* | 26 | ||

| 2D Color Code | 4.29 | Square | 35 | 20 | 168* | 270 | 17 | 132* | 56 |

| Hexagon | 50 | 60 | Time-Limit | 252 | 18 | Time-Limit | 47 | ||

| H-Square | 93 | 72 | Time-Limit | 468 | 26 | Time-Limit | 125 | ||

| H-Hexagon | 115 | 180* | Time-Limit | 1,038 | 30* | Time-Limit | 324 | ||

| 3D Color Code | 3.69 | Square | 30 | 0 | Not Exist | Not Exist | 20 | Not Exist | Not Exist |

| Hexagon | 16 | 4 | Not Exist | Not Exist | 31 | Not Exist | Not Exist | ||

| H-Square | 79 | 14 | Time-Limit | 270 | 30 | Time-Limit | 40 | ||

| H-Hexagon | 55 | 38 | Time-Limit | 228 | 33 | Time-Limit | 35 | ||

| Steane Code | 3.69 | Square | 25 | 0 | Not Exist | Not Exist | 17 | Not Exist | Not Exist |

| Hexagon | 21 | 0 | Not Exist | Not Exist | 18 | Not Exist | Not Exist | ||

| H-Square | 29 | 8 | Not Exist | Not Exist | 32 | Not Exist | Not Exist | ||

| H-Hexagon | 46 | 36 | Time-Limit | 504 | 30 | Time-Limit | 112 | ||

| HGP QLDPC Code | 4.00 | Square | 121 | 588* | Time-Limit | 726 | 70* | Time-Limit | 205 |

| Hexagon | 128 | 876* | Time-Limit | 1,236 | 121* | Time-Limit | 354 | ||

| H-Square | 176 | 859* | Time-Limit | 990 | 96* | Time-Limit | 251 | ||

| H-Hexagon | 265 | 1,275* | Time-Limit | 1,386 | 120* | Time-Limit | 336 | ||

| Surface Code | 3.58 | Square | 289 | 0 | Time-Limit | 9,594 | 8 | Time-Limit | 2,770 |

| Hexagon | 225 | 6,547* | Time-Limit | 8,928 | 391* | Time-Limit | 2,428 | ||

| H-Square | 251 | 288 | Time-Limit | 9,654 | 15 | Time-Limit | 2,458 | ||

| H-Hexagon | 387 | 9,322* | Time-Limit | 11,064 | 450* | Time-Limit | 2,930 | ||

Stabilizer codes: Our evaluation covers both classical and recent popular stabilizer codes to demonstrate the generality of our framework. For instance, small-scale and large-scale surface code are selected to show support for the most popular surface code family. The 2D and the 3D color codes color codes are included to illustrate the influence of distinct code topologies. The classical Steane code is selected for its role as a basic block that can be merged into larger stabilizer codes [21], such as the and color codes. The HyperGraph Product (HGP) code [38] is chosen to demonstrate our framework’s applicability to recent popular qLDPC codes. Moreover, we adopt some manually designed measurement schemes for specific codes to showcase the extensibility of our framework. Specifically, we adapt Shor’s scheme [56] for the 3D color code and the Steane code to ensure the fault tolerance of the ESM circuits.

To quantify the level of interconnectivity for each stabilizer code, we define the density of a stabilizer code:

Error Model: We follow a widely-used circuit-level error model similar to those in [20, 54, 19], involving the same error rates and types. Specifically, we apply probabilities ranging from to to the single-qubit depolarizing error channel for single-qubit gates, the two-qubit depolarizing error channel for two-qubit gates, and the Pauli-X error channel for measurement and reset operations. Additionally, for idle errors induced by decoherence, each idle qubit undergoes a single-qubit depolarizing error channel per gate duration with a probability of [4, 19, 57]. These errors affect all qubits, including both data and ancilla qubits.

Metrics: We consider two key metrics that significantly impact the fidelity of quantum circuit execution and are widely used to evaluate the performance of general QMR method s [32, 31, 33]. (1) Extra CNOT gate count: We evaluate the extra CNOT gate count required by ESM circuits to compensate for sparse architectures. Previous studies [18, 54] and our experiments in Section VI-D show the high sensitivity of ESM circuits to two-qubit gate errors, making the CNOT gate count a crucial factor that significantly affects the fidelity of logical qubits. (2) Circuit Depth: We assess the Circuit Depth of entire ESM circuit, which is the maximum time coordinates of all gates. Due to the limitation of current quantum computing technology, physical qubits can only function well up to a short ‘lifetime’. Thus, minimizing depth becomes crucial to ensure efficiency. A larger time-step count would introduce more decoherence errors that accumulate, eventually surpassing the fault tolerance threshold of the error correction procedure.

VI-B Compared to Swapping-Based Approaches

We begin by comparing QECC-Synth with two traditional swapping-based approaches designed for the QMR task of general quantum circuits: SATmap (a constraint-based approach) [33] and Sabre (a heuristic approach) [31]. The results in Table I demonstrate that our QECC-Synth consistently synthesizes smaller and faster ESM circuits for stabilizer codes. We highlight the following three results:

(1) Our QECC-Synth shows great improvement even when the code synthesis task is small-scale. For instance, in the case of the surface code, QECC-Synth demonstrates an average reduction of 26.5% in the extra CNOT gate count compared to SATmap and 74.9% compared to Sabre. Additionally, the improvement in circuit depth is even more substantial, with an average reduction of 55.5% compared to SATmap and 34.7% compared to Sabre. This highlights the efficiency of QECC-Synth’s bridging-based approach over the traditional swapping-based approach in addressing connectivity disparity problems in ESM circuit synthesis.

(2) The ”” symbol and ”Time-Limit” entry indicate that the SAT solver times out, returns a sub-optimal result, or does not produce a result. This often occurs when the code becomes complicated and large, such as the HGP qLDPC code, or when the ”code-architecture” gap is substantial, such as mapping the dense color code to sparse architectures (Hexagon, Heavy Square, and Heavy Hexagon). This demonstrates that QECC-Synth efficiently prunes the optimization space of ESM circuits by treating and mapping each stabilizer as a whole, rather than mapping each gate in the ESM circuit separately, as traditional QMR approaches do.

(3) The ”Not-Exist” entry indicates that the approach verifies the impossibility of finding a workable code synthesis on a device with the given architecture and a limited number of physical qubits, as the number of physical qubits is always restricted on a practical quantum chiplet [24, 5, 10]. The inability of swapping-based approaches to leverage the flexibility of overlapping ancilla qubits contributes to the occurrence of ”Not-Exist”. These approaches treat data and ancilla qubits as identical, requiring each to be mapped to a distinct physical qubit, which may exceed the available number of physical qubits on the device. For instance, in the case of the 3D Color Code and the Steane Code, their original ESM circuits apply Shor’s scheme and require more than one ancilla qubit for each stabilizer, resulting in a ”Not-Exist” for the swapping-based approaches.

VI-C Compared to Heuristic Bridging-Based Approach

We compare our QECC-Synth with Surf-Stitch [19], a heuristic method that can only work on the surface code and specific regular architectures. In Table II, we show the synthesis results of the surface code on both perfect and defective architectures [42, 43, 44] that have a faulty qubit in the middle due to fabrication defects. The result shows that QECC-Synth has a wider range of applicability while achieving equal or better ESM circuits than Surf-Stitch. We highlight the following three results:

| QECC-Synth | Surf-Stitch | ||||

| # Extra CNOT gate | Circuit depth | # Extra CNOT gate | Circuit depth | ||

| Square | Perfect | 0 | 8 | 0 | 8 |

| Defective | 12 | 17 | |||

| Hexagon | Perfect | 72 | 20 | 120 | 26 |

| Defective | 76 | 17 | |||

| Heavy Square | Perfect | 80 | 15 | 80 | 24 |

| Defective | 94 | 20 | |||

| Heavy Hexagon | Perfect | 216 | 18 | 224 | 40 |

| Defective | 216 | 23 | |||

(1) Although at most cases of perfect architectures, the improvement on CNOT gates number by QECC-Synth is marginal, as the Surf-Stitch’s mannual mapping of surface code is already near optimal, QECC-Synth still find a synthesis on hexagon with using 40% less extra CNOT gates. Moreover, due to our more concurrent scheduling strategy, QECC-Synth achieves a average reduction of 38.5% in circuit depth.

(2) In the presence of faulty physical qubits that cannot be used in ESM circuits due to fabrication defects [42, 58, 43], Surf-Stitch fails to operate because the architecture is no longer regular. However, our QECC-Synth adapts seamlessly to these defective architectures with only a minor increase in CNOT gates and circuit depth.

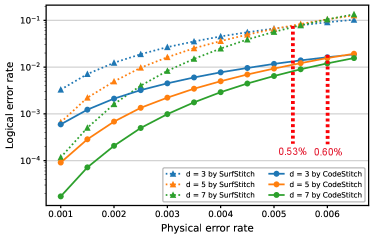

(3) For two synthesized ESM circuits with an equal count of CNOT gates (e.g. perfect heavy-square), circuit depth significantly affects their error correction capability. As shown in Fig. 9, we simulated the logical error rates for surface codes of different distances on the heavy-square architecture, each using slots of simulation. The results for QECC-Synth consistently show significantly lower logical error rates, ranging from 6.8x to 8.6x lower for the distance-7 surface code, despite both approaches using the same number of CNOT gates. Moreover, surface codes synthesized by QECC-Synth also show an improved error threshold. Although the improvement from 0.53% to 0.60% may seem marginal, it significantly affects the scalability of surface codes. For instance, if we aim to implement a logical qubit on a device with a physical error rate of 0.50%, Surf-Stitch would require 10x more physical qubits to achieve the same logical error rate.

VI-D Ablation Study

To justify prioritizing ”# extra CNOT gates” over ”circuit depth” as the primary optimization goal and employing a two-stage SAT approach to optimize them separately, we perform a breakdown analysis of the logical error rate to identify the most critical factor for the fidelity of the ESM circuit. Additionally, we conduct a scalability analysis to demonstrate the performance of our heuristic relaxation method.

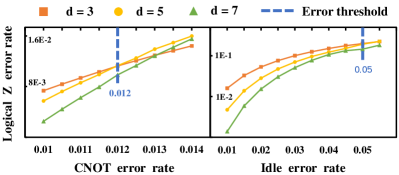

Breakdown analysis of logical error rate. This study provides a breakdown analysis of how the error threshold shifts across two vital error types: two-qubit CNOT gate errors and device idle errors. The simulation focuses on surface codes on 2-D grid hardware, but the conclusion can be readily extrapolated to broader contexts. This analysis provides additional support for the rationale behind prioritizing the reduction of # CNOT gates (linked to accumulated CNOT errors) over circuit depth (linked to accumulated idle errors) when optimizing QEC code synthesis.

We conducted simulation slots for each logical error point. When analyzing the CNOT gate error, the idle error is set to 0, and vice versa. As shown in Fig. 10, pure CNOT gate error exhibits a per-step error threshold of 1.2%, while pure idle error demonstrates a threshold of 5%. The significantly lower threshold for CNOT errors highlights both the reduced tolerance for this type of error and its amplified impact on the overall logical error rate. This emphasizes the importance of prioritizing the reduction of the CNOT gate count.

Scalability Analysis. In this study, we evaluate the scalability of QECC-Synth in comparison to the solver-based SATmap and test our relaxation method by code partition on dense and large-scale stabilizer codes.

| Square | Hexagon | Heavy Square | Heavy Hexagon | ||

| # Variable | QECC-Synth | ||||

| SATmap | |||||

| # Hard clause | QECC-Synth | ||||

| SATmap | |||||

| # Soft clause | QECC-Synth | ||||

| SATmap | |||||

The sizes of the MaxSAT-encoded problem are shown in Table III. It reveals that tasks from SATmap exhibit 1.5x to 8.5x more variables, 20x to 120x more hard constraints, and 50x to 125x more soft constraints than the tasks from QECC-Synth. This indicates that our QECC-Synth method offers a more efficient approach to encoding the QEC code mapping problem than SATmap, by formalizing the special structure characteristic of the measurement circuit in stabilizers.

Moreover, the synthesis results of the HGP qLDPC code and the surface code in Table I further demonstrate the efficiency of QECC-Synth on dense and large-scale stabilizer codes using the heuristic relaxation method. It shows significant improvements in reducing extra CNOT gates and circuit depth compared to traditional swapping-based approaches.

VII Related Work

Swapping-based methods. Extensive research has addressed the challenge of mapping general quantum circuits onto hardware with limited connectivity. These methods typically fall into one of three categories: constraint-based [59, 60, 61, 33], heuristic [31, 62, 63], or a hybrid approach [64]. However, these techniques are inadequate for ESM circuits due to the inserted SWAP gates, which disrupt qubit locations and hinder parallel execution of stabilizer measurements with shared data qubits. Moreover, introducing SWAP gates can elevate the circuit’s error rate, compromising the precision needed for effective ESM circuits.

Bridging-based methods. The original bridging-based methods [21, 35, 65, 66, 37] extend single ancilla qubits into ancilla bridges to alleviate the connectivity constraint. This approach offers fixed qubit locations and introduces fewer additional gates compared to swap-based methods, enhancing performance. However, these methods are designed for single ESM circuits and struggle with complex dependencies among stabilizer measurements within QEC codes. Recent efforts have applied bridging-based techniques to entire QEC codes [67, 20, 19], but they are limited to specific QEC codes and hardware architectures, lacking adaptability to broader settings. Furthermore, these approaches rely on heuristic design without optimality guarantees.

VIII Conclusion

This paper introduces the first automated compilation framework for implementing ESM circuits using the bridging method. Our approach demonstrates broad applicability across diverse QEC codes and hardware architectures, including systems with defective qubits. By systematically classifying and leveraging the primary flexibilities of the bridging method, we effectively explore its extensive design space and formalize ESM circuit implementation as a two-stage MaxSAT problem solved by high-performance SAT solvers. Comparative evaluations show our method significantly outperforms existing swap-based and bridging approaches while achieving superior adaptability. These advancements represent a significant step toward realizing long-term fault-tolerant quantum computing goals.

IX Acknowledgments

We thank the anonymous reviewers for their valuable and constructive feedback. This work was supported in part by NSF 2138437, NSF 2048144, and the Robert N. Noyce Trust. This material is based upon work supported by the U.S. Department of Energy, Office of Science, National Quantum Information Science Research Centers, Quantum Science Center.

References

- [1] John Preskill. Quantum computing in the nisq era and beyond. Quantum, 2018.

- [2] Jerry Chow, Oliver Dial, and Jay Gambetta. Ibm quantum breaks the 100-qubit processor barrier. IBM Research Blog, 2, 2021.

- [3] Adam Holmes, Mohammad Reza Jokar, Ghasem Pasandi, Yongshan Ding, Massoud Pedram, and Frederic T. Chong. Nisq+: Boosting quantum computing power by approximating quantum error correction. 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA), pages 556–569, 2020.

- [4] Exponential suppression of bit or phase errors with cyclic error correction. Nature, 595(7867):383–387, 2021.

- [5] Frank Arute, Kunal Arya, Ryan Babbush, Dave Bacon, Joseph C Bardin, Rami Barends, Rupak Biswas, Sergio Boixo, Fernando GSL Brandao, David A Buell, et al. Quantum supremacy using a programmable superconducting processor. Nature, 574(7779):505–510, 2019.

- [6] Michael A Nielsen and Isaac L Chuang. Quantum computation and quantum information. Cambridge university press, 2010.

- [7] Emanuel Knill, Raymond Laflamme, and Wojciech H Zurek. Resilient quantum computation. Science, 279(5349):342–345, 1998.

- [8] Dorit Aharonov and Michael Ben-Or. Fault-tolerant quantum computation with constant error. In Proceedings of the twenty-ninth annual ACM symposium on Theory of computing, pages 176–188, 1997.

- [9] JF Marques, BM Varbanov, MS Moreira, Hany Ali, Nandini Muthusubramanian, Christos Zachariadis, Francesco Battistel, Marc Beekman, Nadia Haider, Wouter Vlothuizen, et al. Logical-qubit operations in an error-detecting surface code. Nature Physics, 18(1):80–86, 2022.

- [10] Suppressing quantum errors by scaling a surface code logical qubit. Nature, 614(7949):676–681, 2023.

- [11] VV Sivak, Alec Eickbusch, Baptiste Royer, Shraddha Singh, Ioannis Tsioutsios, Suhas Ganjam, Alessandro Miano, BL Brock, AZ Ding, Luigi Frunzio, et al. Real-time quantum error correction beyond break-even. Nature, 616(7955):50–55, 2023.

- [12] A Robert Calderbank and Peter W Shor. Good quantum error-correcting codes exist. Physical Review A, 54(2):1098, 1996.

- [13] Andrew Steane. Multiple-particle interference and quantum error correction. Proceedings of the Royal Society of London. Series A: Mathematical, Physical and Engineering Sciences, 452(1954):2551–2577, 1996.

- [14] Sergey B Bravyi and A Yu Kitaev. Quantum codes on a lattice with boundary. arXiv preprint quant-ph/9811052, 1998.

- [15] Héctor Bombín and Miguel A Martin-Delgado. Optimal resources for topological two-dimensional stabilizer codes: Comparative study. Physical Review A, 76(1):012305, 2007.

- [16] Peter W Shor. Scheme for reducing decoherence in quantum computer memory. Physical review A, 52(4):R2493, 1995.

- [17] A Yu Kitaev. Fault-tolerant quantum computation by anyons. Annals of physics, 303(1):2–30, 2003.

- [18] Austin G Fowler, Matteo Mariantoni, John M Martinis, and Andrew N Cleland. Surface codes: Towards practical large-scale quantum computation. Physical Review A, 86(3):032324, 2012.

- [19] Anbang Wu, Gushu Li, Hezi Zhang, Gian Giacomo Guerreschi, Yufei Ding, and Yuan Xie. A synthesis framework for stitching surface code with superconducting quantum devices. In Proceedings of the 49th Annual International Symposium on Computer Architecture, ISCA ’22, page 337–350, New York, NY, USA, 2022. Association for Computing Machinery.

- [20] Christopher Chamberland, Guanyu Zhu, Theodore J Yoder, Jared B Hertzberg, and Andrew W Cross. Topological and subsystem codes on low-degree graphs with flag qubits. Physical Review X, 10(1):011022, 2020.

- [21] Ben W Reichardt. Fault-tolerant quantum error correction for steane’s seven-qubit color code with few or no extra qubits. Quantum Science and Technology, 6(1):015007, nov 2020.

- [22] Yu Tomita and Krysta M Svore. Low-distance surface codes under realistic quantum noise. Physical Review A, 90(6):062320, 2014.

- [23] Panos Aliferis and Andrew W Cross. Subsystem fault tolerance with the bacon-shor code. Physical review letters, 98(22):220502, 2007.

- [24] Jay Gambetta. Ibm’s roadmap for scaling quantum technology. IBM Research Blog (September 2020), 2020.

- [25] SA Moses, CH Baldwin, MS Allman, R Ancona, L Ascarrunz, C Barnes, J Bartolotta, B Bjork, P Blanchard, M Bohn, et al. A race track trapped-ion quantum processor. arXiv preprint arXiv:2305.03828, 2023.

- [26] Eyob A Sete, Angela Q Chen, Riccardo Manenti, Shobhan Kulshreshtha, and Stefano Poletto. Floating tunable coupler for scalable quantum computing architectures. Physical Review Applied, 15(6):064063, 2021.

- [27] J Stehlik, DM Zajac, DL Underwood, T Phung, J Blair, S Carnevale, D Klaus, GA Keefe, A Carniol, Muir Kumph, et al. Tunable coupling architecture for fixed-frequency transmon superconducting qubits. Physical Review Letters, 127(8):080505, 2021.

- [28] Markus Brink, Jerry M Chow, Jared Hertzberg, Easwar Magesan, and Sami Rosenblatt. Device challenges for near term superconducting quantum processors: frequency collisions. In 2018 IEEE International Electron Devices Meeting (IEDM), pages 6–1. IEEE, 2018.

- [29] Moein Malekakhlagh, Easwar Magesan, and David C McKay. First-principles analysis of cross-resonance gate operation. Physical Review A, 102(4):042605, 2020.

- [30] Jared B Hertzberg, Eric J Zhang, Sami Rosenblatt, Easwar Magesan, John A Smolin, Jeng-Bang Yau, Vivekananda P Adiga, Martin Sandberg, Markus Brink, Jerry M Chow, et al. Laser-annealing josephson junctions for yielding scaled-up superconducting quantum processors. npj Quantum Information, 7(1):129, 2021.

- [31] Gushu Li, Yufei Ding, and Yuan Xie. Tackling the qubit mapping problem for nisq-era quantum devices. In Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems, pages 1001–1014, 2019.

- [32] Bochen Tan and Jason Cong. Optimal layout synthesis for quantum computing. In Proceedings of the 39th International Conference on Computer-Aided Design, pages 1–9, 2020.

- [33] Abtin Molavi, Amanda Xu, Martin Diges, Lauren Pick, Swamit Tannu, and Aws Albarghouthi. Qubit mapping and routing via maxsat. In 2022 55th IEEE/ACM International Symposium on Microarchitecture (MICRO), pages 1078–1091. IEEE, 2022.

- [34] Daniel Gottesman. Theory of fault-tolerant quantum computation. Physical Review A, 57(1):127, 1998.

- [35] Lingling Lao and Carmen G. Almudever. Fault-tolerant quantum error correction on near-term quantum processors using flag and bridge qubits. Phys. Rev. A, 101:032333, Mar 2020.

- [36] Rui Chao and Ben W Reichardt. Quantum error correction with only two extra qubits. Physical review letters, 121(5):050502, 2018.

- [37] Christopher Chamberland and Michael E Beverland. Flag fault-tolerant error correction with arbitrary distance codes. Quantum, 2:53, 2018.

- [38] Jean-Pierre Tillich and Gilles Zémor. Quantum ldpc codes with positive rate and minimum distance proportional to the square root of the blocklength. IEEE Transactions on Information Theory, 60(2):1193–1202, 2013.

- [39] Anirudh Krishna and David Poulin. Fault-tolerant gates on hypergraph product codes. Physical Review X, 11(1):011023, 2021.

- [40] Thomas M Stace, Sean D Barrett, and Andrew C Doherty. Thresholds for topological codes in the presence of loss. Physical review letters, 102(20):200501, 2009.

- [41] Thomas M Stace and Sean D Barrett. Error correction and degeneracy in surface codes suffering loss. Physical Review A, 81(2):022317, 2010.

- [42] James M Auger, Hussain Anwar, Mercedes Gimeno-Segovia, Thomas M Stace, and Dan E Browne. Fault-tolerance thresholds for the surface code with fabrication errors. Physical Review A, 96(4):042316, 2017.

- [43] Sophia Fuhui Lin, Joshua Viszlai, Kaitlin N Smith, Gokul Subramanian Ravi, Charles Yuan, Frederic T Chong, and Benjamin J Brown. Codesign of quantum error-correcting codes and modular chiplets in the presence of defects. In Proceedings of the 29th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2, pages 216–231, 2024.

- [44] Yasunari Suzuki, Takanori Sugiyama, Tomochika Arai, Wang Liao, Koji Inoue, and Teruo Tanimoto. Q3de: A fault-tolerant quantum computer architecture for multi-bit burst errors by cosmic rays. In 2022 55th IEEE/ACM International Symposium on Microarchitecture (MICRO), pages 1110–1125. IEEE, 2022.

- [45] Armin Biere, Marijn Heule, and Hans van Maaren. Handbook of satisfiability, volume 185. IOS press, 2009.

- [46] Ivan B Djordjevic. Quantum information processing, quantum computing, and quantum error correction: an engineering approach. Academic Press, 2021.

- [47] Emanuel Knill and Raymond Laflamme. Theory of quantum error-correcting codes. Physical Review A, 55(2):900, 1997.

- [48] Andrew M Steane. Quantum reed-muller codes. IEEE Transactions on Information Theory, 45(5):1701–1703, 1999.

- [49] Daniel M Greenberger, Michael A Horne, and Anton Zeilinger. Going beyond bell’s theorem. In Bell’s theorem, quantum theory and conceptions of the universe, pages 69–72. Springer, 1989.

- [50] Chin Yang Lee. An algorithm for path connections and its applications. IRE transactions on electronic computers, (3):346–365, 1961.

- [51] Konstantin Andreev and Harald Räcke. Balanced graph partitioning. In Proceedings of the sixteenth annual ACM symposium on Parallelism in algorithms and architectures, pages 120–124, 2004.

- [52] Jiongzhi Zheng, Kun He, Jianrong Zhou, Yan Jin, Chumin Li, and Felip Manyà. Incorporating multi-armed bandit with local search for maxsat. ArXiv, abs/2211.16011, 2022.

- [53] Alexey Ignatiev, Antonio Morgado, and Joao Marques-Silva. PySAT: A Python toolkit for prototyping with SAT oracles. In SAT, pages 428–437, 2018.

- [54] Craig Gidney. Stim: a fast stabilizer circuit simulator. Quantum, 5:497, 2021.

- [55] Oscar Higgott. Pymatching: A python package for decoding quantum codes with minimum-weight perfect matching. ACM Transactions on Quantum Computing, 3(3):1–16, 2022.

- [56] David P DiVincenzo and Panos Aliferis. Effective fault-tolerant quantum computation with slow measurements. Physical review letters, 98(2):020501, 2007.

- [57] Poulami Das, Swamit Tannu, Siddharth Dangwal, and Moinuddin Qureshi. Adapt: Mitigating idling errors in qubits via adaptive dynamical decoupling. In MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture, pages 950–962, 2021.

- [58] Shota Nagayama, Austin G Fowler, Dominic Horsman, Simon J Devitt, and Rodney Van Meter. Surface code error correction on a defective lattice. New Journal of Physics, 19(2):023050, 2017.

- [59] Robert Wille, Lukas Burgholzer, and Alwin Zulehner. Mapping quantum circuits to ibm qx architectures using the minimal number of swap and h operations. In Proceedings of the 56th Annual Design Automation Conference 2019, pages 1–6, 2019.

- [60] Prakash Murali, Jonathan M Baker, Ali Javadi-Abhari, Frederic T Chong, and Margaret Martonosi. Noise-adaptive compiler mappings for noisy intermediate-scale quantum computers. In Proceedings of the twenty-fourth international conference on architectural support for programming languages and operating systems, pages 1015–1029, 2019.

- [61] Bochen Tan and Jason Cong. Optimal layout synthesis for quantum computing. In Proceedings of the 39th International Conference on Computer-Aided Design, pages 1–9, 2020.

- [62] Alwin Zulehner, Alexandru Paler, and Robert Wille. An efficient methodology for mapping quantum circuits to the ibm qx architectures. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 38(7):1226–1236, 2018.

- [63] Chi Zhang, Ari B Hayes, Longfei Qiu, Yuwei Jin, Yanhao Chen, and Eddy Z Zhang. Time-optimal qubit mapping. In Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, pages 360–374, 2021.

- [64] Will Finigan, Michael Cubeddu, Thomas Lively, Johannes Flick, and Prineha Narang. Qubit allocation for noisy intermediate-scale quantum computers. arXiv preprint arXiv:1810.08291, 2018.

- [65] Rui Chao and Ben W Reichardt. Flag fault-tolerant error correction for any stabilizer code. PRX Quantum, 1(1):010302, 2020.

- [66] Rui Chao and Ben W Reichardt. Fault-tolerant quantum computation with few qubits. npj Quantum Information, 4(1):42, 2018.

- [67] Maxime A Tremblay, Nicolas Delfosse, and Michael E Beverland. Constant-overhead quantum error correction with thin planar connectivity. Physical Review Letters, 129(5):050504, 2022.